Adv ance informa t ion – Texas Instruments TMS320 User Manual

Page 53

TMS320C25

SPRS010B — MAY 1987 — REVISED NOVEMBER 1990

POST OFFICE BOX 1443

HOUSTON, TEXAS 77001

53

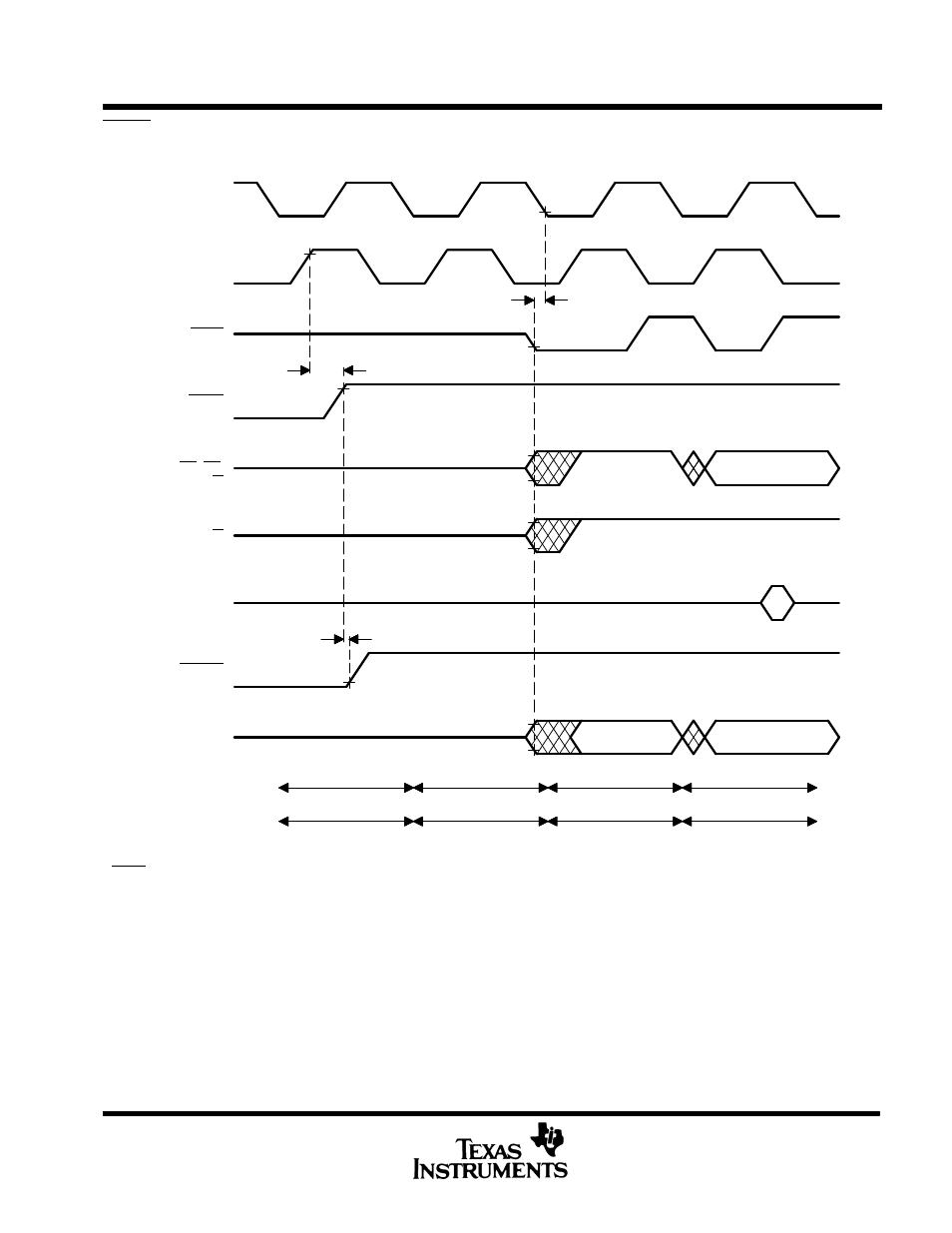

HOLD timing (part B)

CLKOUT1

CLKOUT2

STRB

HOLD

PS, DS,

or IS

R/W

D15-D0

HOLDA

A15-A0

FETCH

EXECUTE

t

d(C2H-H)

†

In

N + 2

N + 2

Valid

--

--

--

N + 2

--

--

--

N + 1

t

en(A-C1L)

t

d(HH-AH)

†

HOLD is an asynchronous input and can occur at any time during a clock cycle. If the specified timing is met, the exact sequence shown will occur;

otherwise, a delay of one CLKOUT2 cycle will occur.

ADV

ANCE

INFORMA

T

ION