Adv ance informa t ion – Texas Instruments TMS320 User Manual

Page 38

TMS320C25 50

SPRS010B — MAY 1987 — REVISED NOVEMBER 1990

POST OFFICE BOX 1443

HOUSTON, TEXAS 77001

38

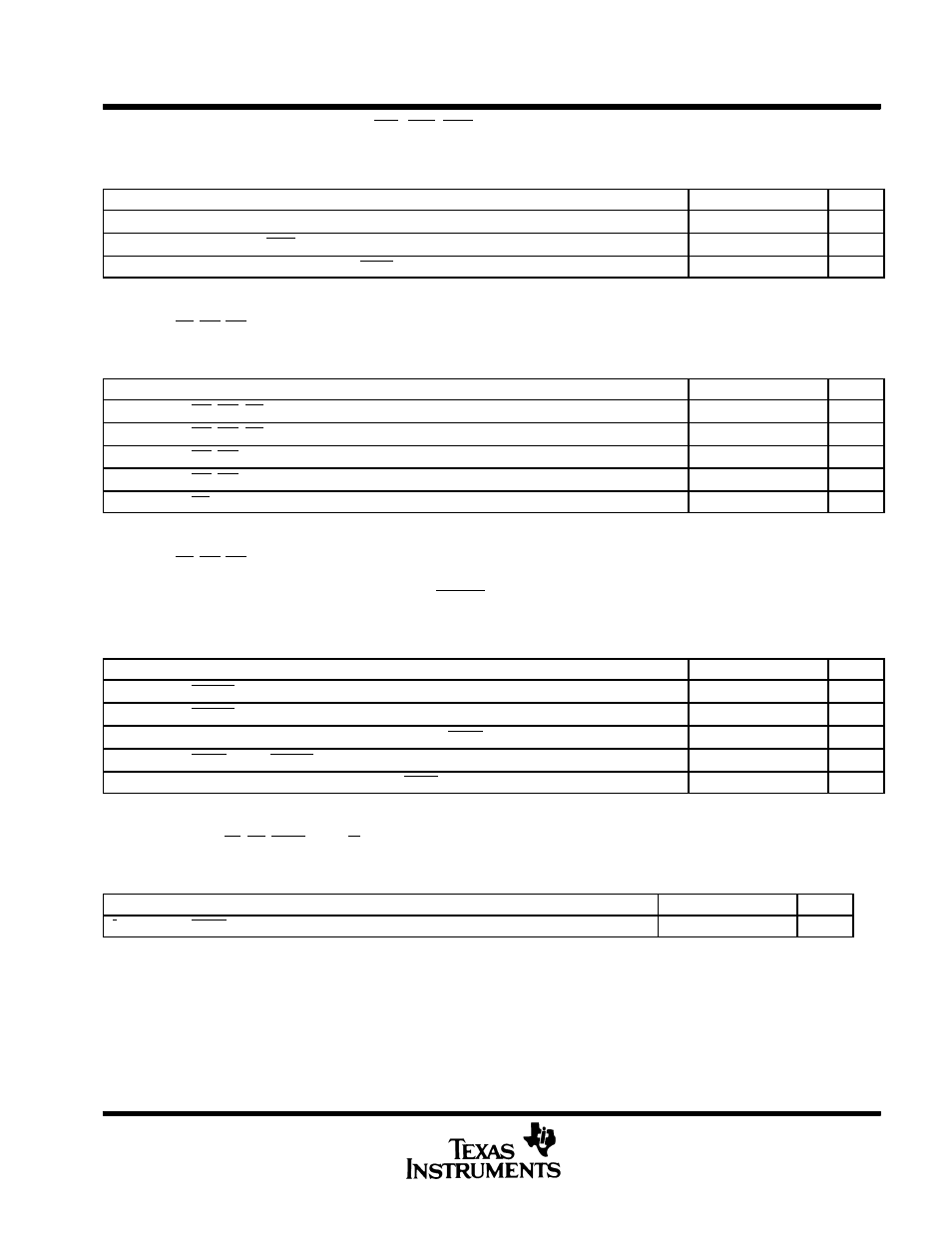

RS, INT, BIO, AND XF TIMING

switching characteristics over recommended operating conditions (see Notes 3 and 16)

PARAMETER

MIN

TYP

MAX

UNIT

t

d(RS)

CLKOUT1 low to reset state entered

22

†

ns

t

d(IACK)

CLKOUT1 to IACK valid

-- 5

7

ns

t

d(XF)

XF valid before falling edge of STRB

Q -- 8

ns

†

Value derived from characterization data and not tested.

NOTES: 3. Q = 1/4 t

c(C)

16. RS, INT, BIO are asynchronous inputs and can occur at any time during a clock cycle.

timing requirements over recommended operating conditions (see Notes 3 and 16)

MIN

NOM

MAX

UNIT

t

su(IN)

INT, BIO, RS setup before CLKOUT1 high

25

ns

t

h(IN)

INT, BIO, RS hold after CLKOUT1 high

0

ns

t

f(IN)

INT, BIO fall time

8

†

ns

t

w(IN)

INT, BIO low pulse duration

t

c(C)

ns

t

w(RS)

RS low pulse duration

3t

c(C)

ns

†

Value derived from characterization data and not tested.

NOTES: 3. Q = 1/4 t

c(C)

16. RS, INT, BIO are asynchronous inputs and can occur at any time during a clock cycle.

HOLD TIMING

switching characteristics over recommended operating conditions (see Note 3)

PARAMETER

MIN

TYP

MAX

UNIT

t

d(CIL-AL)

HOLDA low after CLKOUT1 low

1

†

11

ns

t

dis(AL-A)

HOLDA low to address high-impedance

0

†

ns

t

dis(CIL-A)

Address high-impedance after CLKOUT1 low (HOLD mode, see Note 17)

20

†

ns

t

d(HH-AH)

HOLD high to HOLDA high

19

ns

t

en(A-CIL)

Address driven before CLKOUT1 low (HOLD mode, see Note 17)

8

†

ns

†

Value derived from characterization data and not tested.

NOTES: 3. Q = 1/4 t

c(C)

17. A15-A0, PS, DS, STRB, and R/W timings are all included in timings referenced as “address”.

timing requirements over recommended operating conditions (see Note 3)

MIN

NOM

MAX

UNIT

t

d(C2H-H)

HOLD valid after CLKOUT2 high

Q -- 19

ns

NOTE 3: Q = 1/4 t

c(C)

ADV

ANCE

INFORMA

T

ION