Tms320 second generation digital signal processors – Texas Instruments TMS320 User Manual

Page 16

D

NO.

WORDS

DESCRIPTION

INSTRUCTION BIT CODE

MNEMONIC

D

D

D

D

D

D

B

D

D

K

TMS320 SECOND GENERATION

DIGITAL SIGNAL PROCESSORS

SPRS010B — MAY 1987 — REVISED NOVEMBER 1990

POST OFFICE BOX 1443

HOUSTON, TEXAS 77001

16

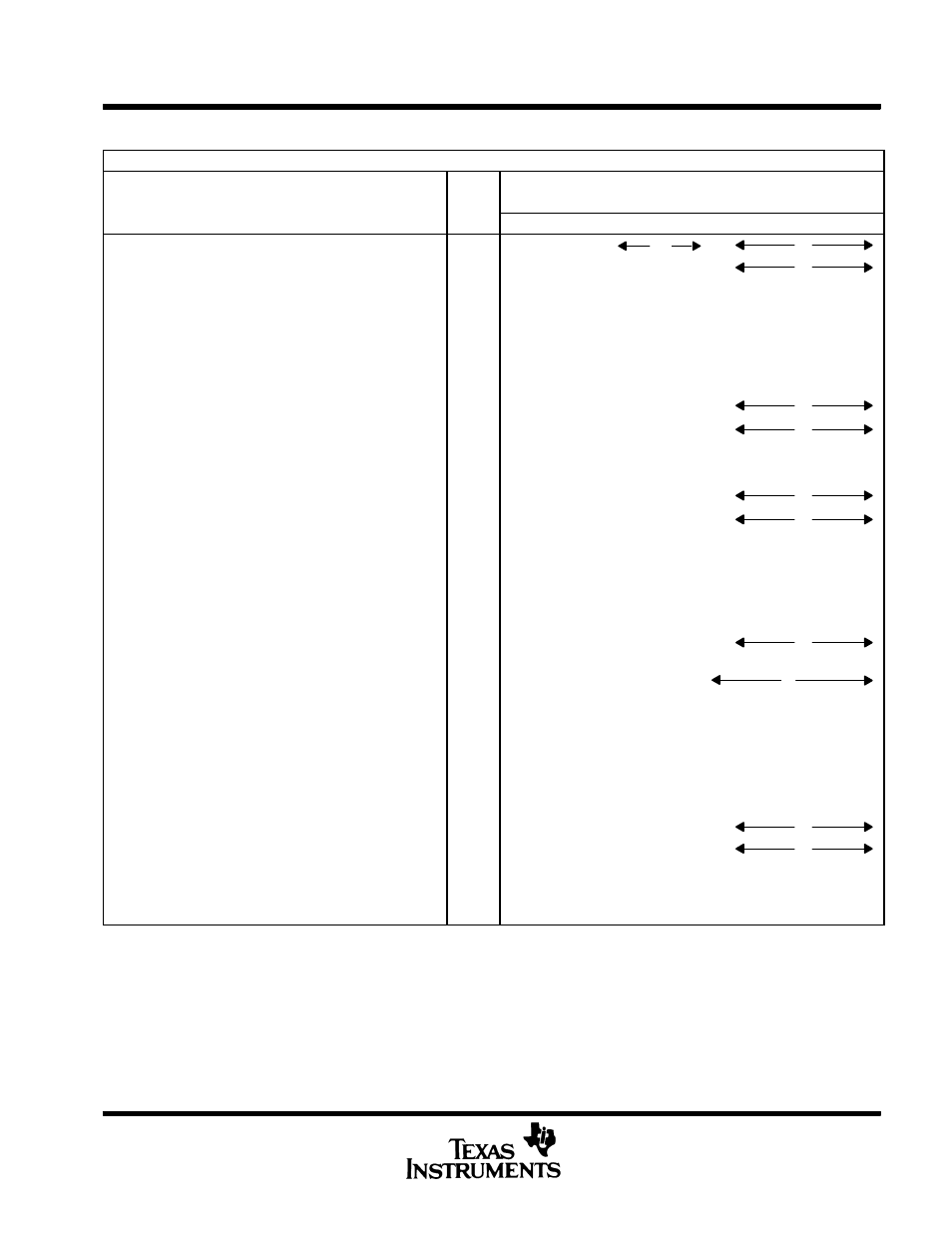

Table 3. TMS320C25 Instruction Set Summary (concluded)

CONTROL INSTRUCTIONS

15 14 13 12 11 10 9

8 7

6 5

4 3

2 1

0

BIT

†

Test bit

1

1

0

0

1

I

BITT

†

Test bit specified by T register

1

0

1

0

1

0

1

1

1

I

CNFD

†

Configure block as data memory

1

1

1

0

0

1

1

1

0 0

0 0

0 0

1 0

0

CNFP

†

Configure block as program memory

1

1

1

0

0

1

1

1

0 0

0 0

0 0

1 0

1

DINT

Disable interrupt

1

1

1

0

0

1

1

1

0 0

0 0

0 0

0 0

1

EINT

Enable interrupt

1

1

1

0

0

1

1

1

0 0

0 0

0 0

0 0

0

IDLE

†

Idle until interrupt

1

1

1

0

0

1

1

1

0 0

0 0

1 1

1 1

1

LST

Load status register STO

1

0

1

0

1

0

0

0

0

I

LST1

†

Load status register ST1

1

0

1

0

1

0

0

0

1

I

NOP

No operation

1

0

1

0

1

0

1

0

1 0

0 0

0 0

0 0

0

POP

Pop top of stack to low accumulator

1

1

1

0

0

1

1

1

0 0

0 0

1 1

1 0

1

POPD

†

Pop top of stack to data memory

1

0

1

1

1

1

0

1

0

I

PSHD

†

Push data memory value onto stack

1

0

1

0

1

0

1

0

0

I

PUSH

Push low accumulator onto stack

1

1

1

0

0

1

1

1

0 0

0 0

1 1

1 0

0

RC

‡

Reset carry bit

1

1

1

0

0

1

1

1

0 0

0 1

1 0

0 0

0

RHM

‡

Reset hold mode

1

1

1

0

0

1

1

1

0 0

0 1

1 1

0 0

0

ROVM

Reset overflow mode

1

1

1

0

0

1

1

1

0 0

0 0

0 0

0 1

0

RPT

†

Repeat instruction as specified by data

memory value

1

0

1

0

0

1

0

1

1

I

RPTK

†

Repeat instruction as specified by immediate

value

1

1

1

0

0

1

0

1

1

RSXM

†

Reset sign-extension mode

1

1

1

0

0

1

1

1

0 0

0 0

0 0

1 1

0

RTC

‡

Reset test/control flag

1

1

1

0

0

1

1

1

0 0

0 1

1 0

0 1

0

SC

‡

Set carry bit

1

1

1

0

0

1

1

1

0 0

0 1

1 0

0 0

1

SHM

‡

Set hold mode

1

1

1

0

0

1

1

1

0 0

0 1

1 1

0 0

1

SOVM

Set overflow mode

1

1

1

0

0

1

1

1

0 0

0 0

0 0

0 1

1

SST

Store status register ST0

1

0

1

1

1

1

0

0

0

I

SST1

†

Store status register ST1

1

0

1

1

1

1

0

0

1

I

SSXM

†

Set sign-extension mode

1

1

1

0

0

1

1

1

0 0

0 0

0 0

1 1

1

STC

‡

Set test/control flag

1

1

1

0

0

1

1

1

0 0

0 1

1 0

0 1

1

TRAP

†

Software interrupt

1

1

1

0

0

1

1

1

0 0

0 0

1 1

1 1

0

†

These instructions are not included in the TMS320C1x instruction set.

‡

These instructions are not included in the TMS32020 instruction set.