System clock options, Table a-8 – Paradyne U8777 User Manual

Page 114

A. Configuration Options

A-18

May 2002

8700-A2-GB20-40

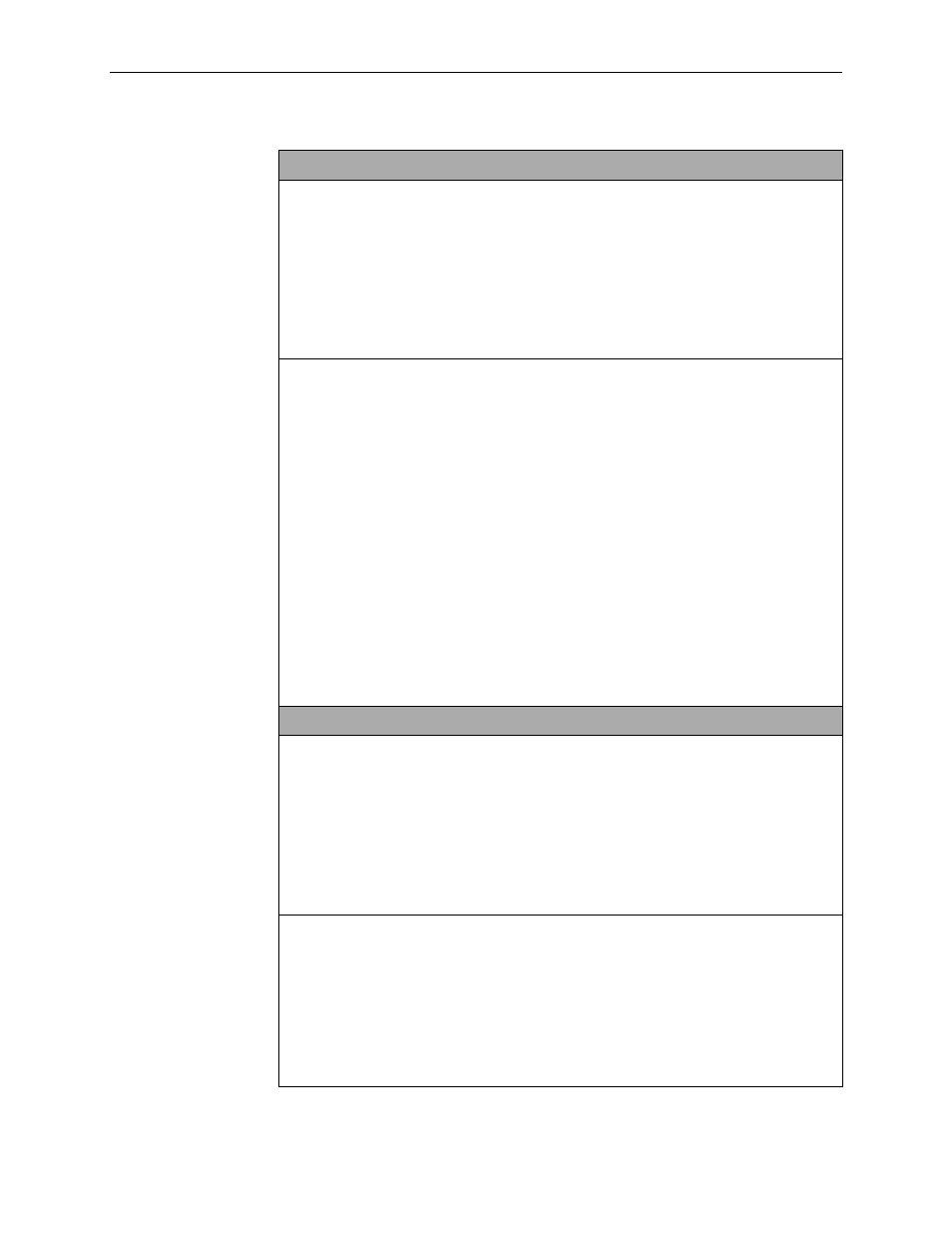

Table A-8.

System Clock Options

Primary System Clock Reference

Possible Settings (LTU, Model 8777): DSX-1 Port 1, DSX-1 Port 2, DSX-1 Port 3,

DSX-1 Port 4, DSX-1 Port 5, DSX-1 Port 6, DSX-1 Port 7, DSX-1 Port 8, Internal

Default Setting: Internal

Possible Settings (LTU, Model 8779): G.703 Port 1, G.703 Port 2, G.703 Port 3,

G.703 Port 4, G.703 Port 5, G.703 Port 6, G.703 Port 7, G.703 Port 8, Internal

Default Setting: Internal

Possible Settings (NTU): DSL Port 1, DSL Port 2, DSL Port 3, DSL Port 4, DSL Port 5,

DSL Port 6, DSL Port 7, DSL Port 8

Default Setting: DSL Port 1

Determines the source of system timing. Select the most accurate clock available.

DSX-1 Port

n

(Model 8777) – Timing is derived from the specified port. To be a valid clock

source, the port must be enabled and must derive its timing from the DSX-1 network.

NOTE: If the DSX-1 port is configured for Bypass mode, the Primary Clock Source

configuration option on the DSX-1 Interface Options screen must be set to DSX-1, not

Internal (see

). All ports configured as system clock sources must be

traceable to the same clock reference.

G.703 Port

n

(Model 8779) – Timing is derived from the specified port. To be a valid clock

source, the port must be enabled and must derive its timing from the G.703 network.

NOTE: If the G.703 port is configured for Bypass mode, the Primary Clock Source

configuration option on the G.703 Interface Options screen must be set to G.703, not

Internal (see

). All ports configured as system clock sources must be

traceable to the same clock reference.

DSL Port

n

– Timing is derived from the specified port. The port must be enabled and in a

cross-connection.

Internal – Timing is derived from the internal oscillator, which provides a Stratum 4

reference.

Secondary System Clock Reference

Possible Settings (LTU, Model 8777): DSX-1 Port 1, DSX-1 Port 2, DSX-1 Port 3,

DSX-1 Port 4, DSX-1 Port 5, DSX-1 Port 6, DSX-1 Port 7, DSX-1 Port 8, Internal

Default Setting: Internal

Possible Settings (LTU, Model 8779): G.703 Port 1, G.703 Port 2, G.703 Port 3,

G.703 Port 4, G.703 Port 5, G.703 Port 6, G.703 Port 7, G.703 Port 8, Internal

Default Setting: Internal

Possible Settings (NTU): DSL Port 1, DSL Port 2, DSL Port 3, DSL Port 4, DSL Port 5,

DSL Port 6, DSL Port 7, DSL Port 8

Default Setting: DSL Port 1

Determines the source of system timing if the primary system clock source fails. If the

secondary clock source fails, the unit switches to the internal clock.

DSX-1 or G.703 Port

n

– Timing is derived from the specified port. To be a valid clock

source, the port must be enabled and must derive its timing from the DSX-1 or G.703

network.

DSL Port

n

– Timing is derived from the specified port. The port must be enabled.

Internal – Timing is derived from the internal oscillator, which provides a Stratum 4

reference.