Table 5-4 – IBM POWERPC 750GL User Manual

Page 193

User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_05.fm.(1.2)

March 27, 2006

Memory Management

Page 193 of 377

The state saved by the processor for each of these exceptions contains information that identifies the address

of the failing instruction. See Chapter 4, Exceptions, on page 151 for a more detailed description of exception

processing.

In addition to the translation exceptions, there are other MMU-related conditions (some of them defined as

implementation-specific, and therefore not required by the architecture) that can cause an exception to occur.

These exception conditions map to processor exceptions as shown in Table 5-4. The only MMU exception

conditions that occur when MSR[DR] = 0 are those that cause an alignment exception for data accesses. For

more detailed information about the conditions that cause an alignment exception (in particular for

string/multiple instructions), see Section 4.5.6, Alignment Exception (0x00600), on page 170.

Notes:

• Some exception conditions depend upon whether the memory area is set up as write-though (W = 1) or

caching-inhibited (I = 1).

• These bits are described fully in “Memory/Cache Access Attributes,” in Chapter 5, “Cache Model and

Memory Coherency,” of the PowerPC Microprocessor Family: The Programming Environments Manual.

• Also see Chapter 4, Exceptions, on page 151 and Chapter 6, “Exceptions,” in the PowerPC Microproces-

sor Family: The Programming Environments Manual for a complete description of the SRR1 and DSISR

bit settings for these exceptions.

Instruction fetch from direct-store seg-

ment

Attempt to fetch instruction when SR[T] = 1

ISI exception

SRR1[3] =1

Data access to direct-store segment

(including floating-point accesses)

Attempt to perform load or store (including floating-point

(FP) load or store) when SR[T] = 1

DSI exception

DSISR[5] =1

Instruction fetch from guarded memory

Attempt to fetch instruction when MSR[IR] = 1 and either

matching xBAT[G] = 1, or no matching BAT entry and

PTE[G] = 1

ISI exception

SRR1[3] =1

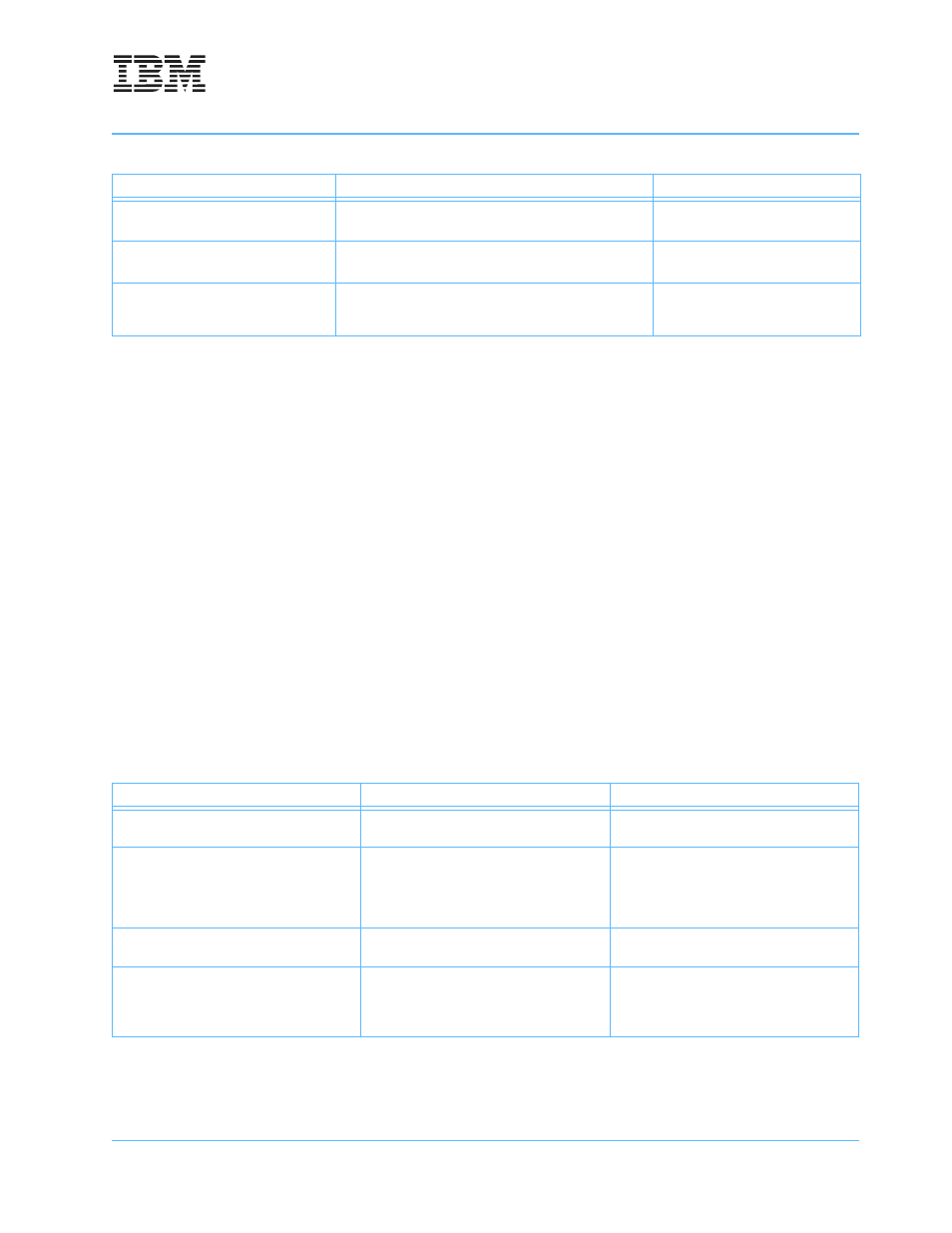

Table 5-4. Other MMU Exception Conditions for the 750GX Processor

(Page 1 of 2)

Condition

Description

Exception

Data Cache Block Set to Zero (dcbz) with

W = 1 or I = 1

dcbz instruction to write-through or cache-

inhibited segment or block

Alignment exception (not required by archi-

tecture for this condition)

Load Word and Reserve Indexed (lwarx),

Store Word Conditional Indexed (stwcx).,

External Control In Word Indexed (eciwx),

or External Control Out Word Indexed

(ecowx) instruction to direct-store segment

Reservation instruction or external control

instruction when SR[T] = 1

DSI exception

DSISR[5] = 1

Floating-point load or store to direct-store

segment

Floating-point memory access when SR[T]

=1

See data access to direct-store segment in

Table 5-3 on page 192.

Load or store that results in a direct-store

error

A DSI exception is taken when a load or

store is attempted to a direct-store segment

(SR[T] = 1)

DSI exception

For additional information, see

Section 4.5.3, DSI Exception (0x00300), on

page 169.

Table 5-3. Translation Exception Conditions

(Page 2 of 2)

Condition Description

Exception