HP Vectra VL 5/xxx Series 5 User Manual

Page 26

26

2 System Board

Chip-Set

Super I/O Chip (

37C932

)

The Super I/O chip (FDC37C932) is contained within a 160-pin PQFP

package. The chip provides the control for the following devices.

Serial / parallel

communications ports

The two 9-pin serial ports (whose pin layouts are depicted on page 58)

support RS-232-C and are buffered by 16550 UARTs, with 16 Byte FIFOs.

They can be programmed as COM1, COM2, COM3, COM4, or disabled.

The 25-pin parallel port (also depicted on page 58) is Centronics

compatible, supporting IEEE 1284. It can be programmed as LPT1, LPT2, or

disabled. It can operate the four modes:

❒ Standard mode (PC/XT, PC/AT, and PS/2 compatible).

❒ Bidirectional mode (PC/XT, PC/AT, and PS/2 compatible).

❒ Enhanced mode (enhanced parallel port, EPP, compatible).

❒ High speed mode (MS/HP extended capabilities port, ECP, compatible).

FDC

The integrated flexible drive controller (FDC) supports any combination of

two from the following: tape drives, 3.5-inch flexible disk drives, 5.25-inch

flexible disk drives. It is software and register compatible with the 82077AA,

and 100% IBM compatible. It has an A and B drive-swapping capability and a

non-burst DMA option.

Keyboard and Mouse

Controller

The computer has an 8042-based keyboard and mouse controller. The

connector pin layouts are shown on page 58. The Windows 95 keyboard is

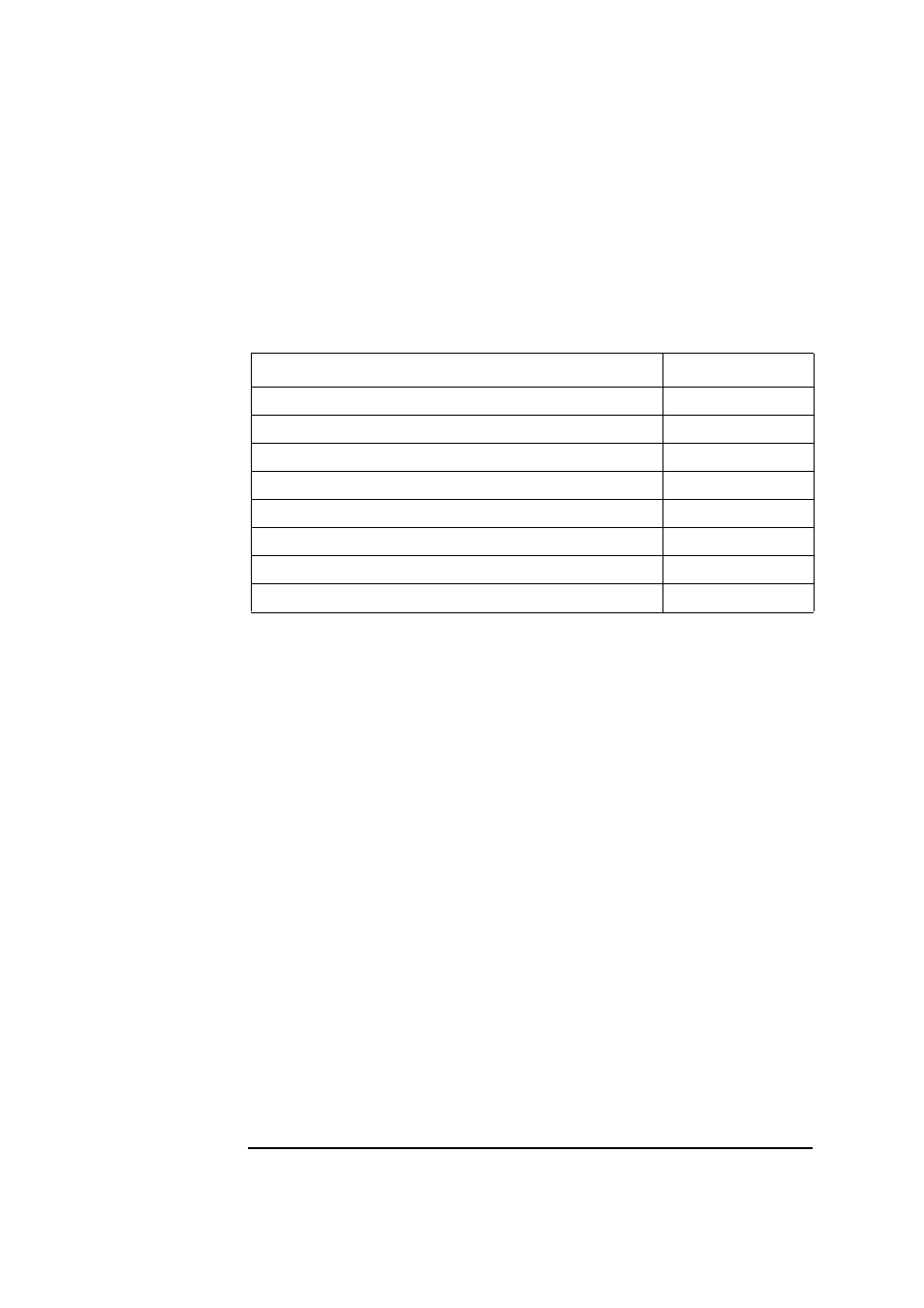

Function

Logical device number

Flexible disk controller

0

Parallel port controller

3

UART1 controller

4

UART2 controller

5

RTC

6

Keyboard controller

7

Mouse controller

7

General purpose I/O (GPIO)

8