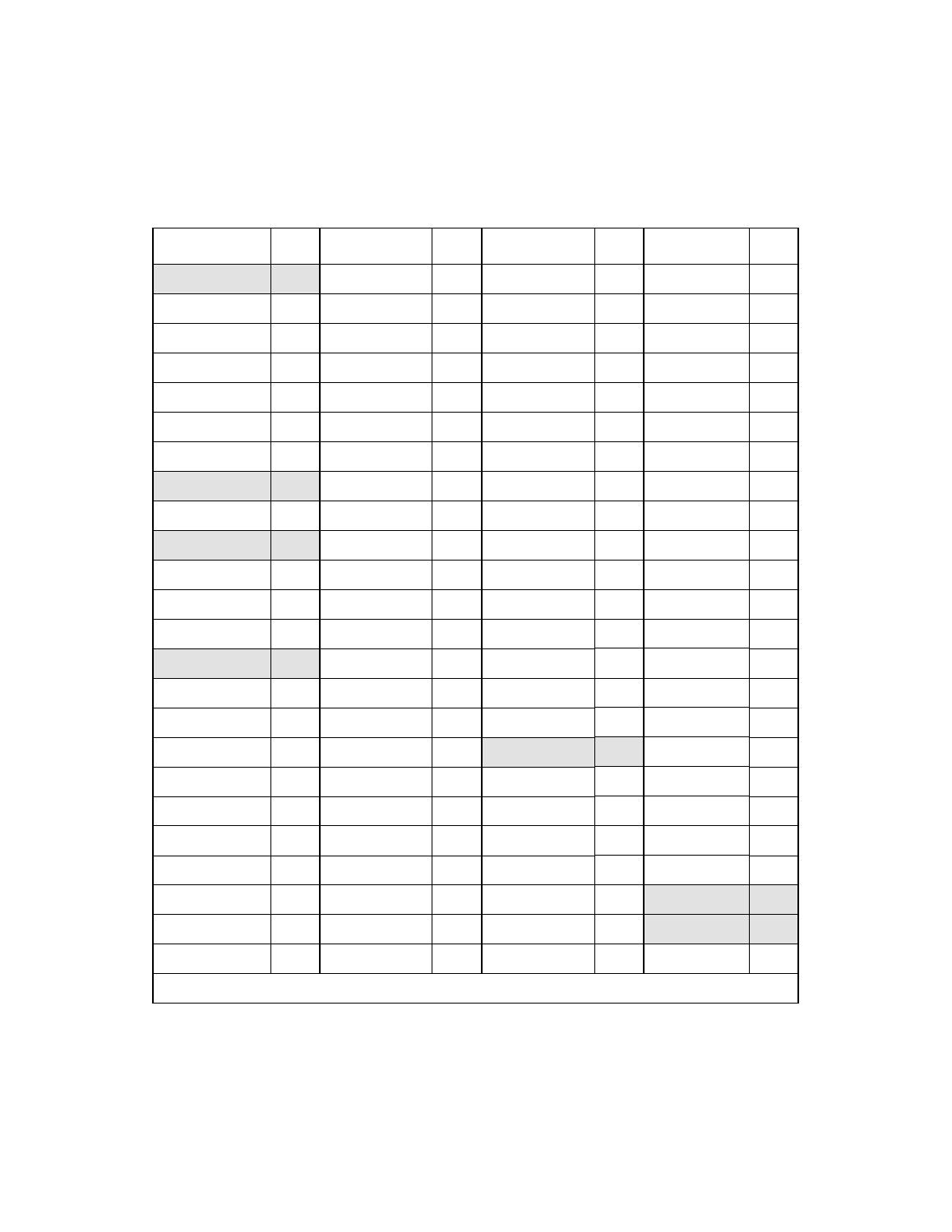

Table 3.1 pci connector j1 (front), Pci connector j1 (front) – Avago Technologies LSI21040 User Manual

Page 49

Operational Environment

3-5

Table 3.1

PCI Connector J1 (Front)

Signal Name

Pin

Signal Name

Pin

Signal Name

Pin

Signal Name

Pin

−

12 V

1

+3.3 V

25

M66EN

49

AD59

71

TCK

2

C_BE3/

26

KEYWAY

50

AD57

72

GND

3

AD23

27

KEYWAY

51

GND

73

TDO

4

GND

28

AD08

52

AD55

74

+5 V

5

AD21

29

AD07

53

AD53

75

+5 V

6

AD19

30

+3.3 V

54

GND

76

INTB/

7

+3.3 V

31

AD05

55

AD51

77

INTD/

8

AD17

32

AD03

56

AD49

78

GND (PRSNT1/)

9

C_BE2/

33

GND

57

+3 V / +5 V

79

RESERVED

10

GND

34

AD01

58

AD47

80

GND (PRSNT2/)

11

IRDY/

35

+3 V / +5 V

59

AD45

81

KEYWAY

12

+3.3 V

36

ACK64/

60

GND

82

KEYWAY

13

DEVSEL/

37

+5 V

61

AD43

83

RESERVED

14

GND

38

+5 V

62

AD41

84

GND

15

LOCK/

39

KEYWAY

xx

GND

85

CLK

16

PERR/

40

KEYWAY

xx

AD39

86

GND

17

+3.3 V

41

RESERVED

63

AD37

87

REQ/

18

SERR/

42

GND

64

+3 V / +5 V

88

+3 V / +5 V

19

+3.3 V

43

C_BE6/

65

AD35

89

AD31

20

C_BE1/

44

C_BE4/

66

AD33

90

AD29

21

AD14

45

GND

67

GND

91

GND

22

GND

46

AD63

68

RESERVED

92

AD27

23

AD12

47

AD61

69

RESERVED

93

AD25

24

AD10

48

+3 V / +5 V

70

GND

94

Note: Highlighted signals are not connected.

- MGA-725M4 (4 pages)

- MGA-71543 (4 pages)

- MGA-71543 (3 pages)

- MGA-82563 (6 pages)

- 3ware 9690SA-8I (Channel) (138 pages)

- 3ware 9690SA-8I (Channel) (380 pages)

- 3ware SAS 9750-8i (48 pages)

- 3ware SAS 9750-8i (29 pages)

- 3ware 9550SXU-8LP (Channel) (149 pages)

- 3ware 9550SXU-8LP (Channel) (40 pages)

- 3ware 9650SE-8LPML (Channel) (45 pages)

- 3ware 9690SA-8I (Channel) (27 pages)

- 3ware 9690SA-8I (Channel) (361 pages)

- 6160 SAS Switch (2 pages)

- Cache Protection for RAID Controller Cards (13 pages)

- MegaRAID SAS 9271-8iCC (13 pages)

- MegaRAID SAS 9361-8i (13 pages)

- MegaRAID SAS 9266-8i (12 pages)

- MegaRAID SAS 9380-8e (43 pages)

- Cache Protection for RAID Controller Cards (139 pages)

- MegaRAID SafeStore Software (502 pages)

- MegaRAID SAS 9285-8ecv (80 pages)

- MegaRAID SAS 9285-8ecv (92 pages)

- MegaRAID SAS 9266-8i (20 pages)

- MegaRAID SAS 9271-8iCC (26 pages)

- MegaRAID SAS 9271-8i (8 pages)

- MegaRAID SAS 0260CV-4i (72 pages)

- MegaRAID SAS 0260CV-4i (64 pages)

- MegaRAID SAS 0260CV-4i (49 pages)

- MegaRAID SAS 9361-8i (7 pages)

- MegaRAID SAS 9341-8i (8 pages)

- MegaRAID SAS 9380-4i4e (7 pages)

- MegaRAID SAS 9380-8e (7 pages)

- MegaRAID SAS 0260CV-4i (28 pages)

- MegaRAID SAS 9240-8i (4 pages)

- MegaRAID SAS 9280-24i4e (14 pages)

- MegaRAID SAS 9280-24i4e (16 pages)

- MegaRAID SAS 9260-16i (12 pages)

- MegaRAID SAS 9280-8e (22 pages)

- MegaRAID SAS 9260-8i (4 pages)

- MegaRAID SafeStore Software (8 pages)

- MegaRAID SAS 9261-8i (4 pages)

- MegaRAID SAS 9285-8e (12 pages)

- MegaRAID SAS 9280-16i4e (12 pages)

- MegaRAID SAS 9280-4i4e (4 pages)