Verilink QPRI 2921 (880-503143-001) Product Manual User Manual

Page 56

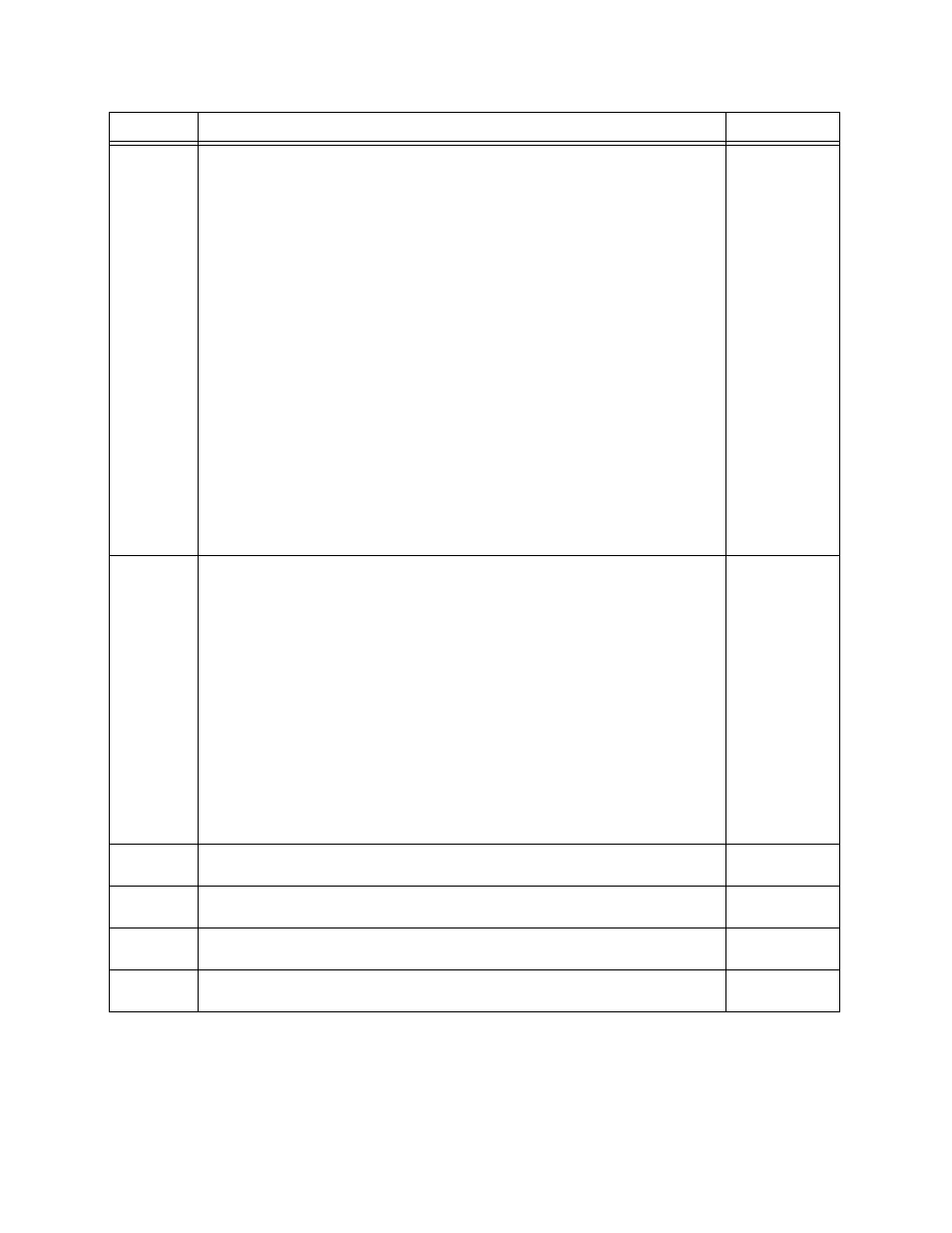

Configuring the QPRI 2921 Via the NCM 2000 Craft Interface

3-22

Verilink QPRI 2921

When finished configuring the T1 port diagnostics parameters,

enter X to return to the Diagnostics Menu.

Tn

Test Pattern:

None: This option indicates that no test pattern will be used.

3 in 24: 3-in-24 Onrs test pattern which consists of three pulses in every 24-

bit sequence (10001000 10000000 00000000). This stress test is useful for

testing circuits under extremely low density conditions. This is mostly useful

for T1 AMI.

QRSS: Quasi-Random Signal Sequence that limits the signal to a maximum of

15 zeros that can be transmitted sequentially. These signals contain a

medley of 20-bit words (except for more than 15 consecutive 0s). It repeats

every 1,048,575 bits. Also, it contains high density sequences and low

density sequences, and sequences that change from low density to high

density and vice versa (as defined by ANSI T1.403).

2

20

-1: Tests circuits for equalization and timing. It is the same as QRSS, but

without the 15 zeros restriction.

1/8: This pattern tests the ability of a circuit to support a pattern having the

minimum ones density (containing 7 zeros indicating empty pulses and 1

pulse-1000000). It helps discover a timing recovery problem. This is mostly

useful for T1 AMI.

2

15

-1: This pattern tests circuits for equalization and timing using an

alternate pattern for jitter testing. The pattern repeats every 32,757 bits.

All 0s: This pattern is composed entirely of framed zeros (00000000). It

should only be used in conjunction with B8ZS (a clear channel) for end-to-

end testing. This is mostly useful for T1 B8ZS.

1) NONE

2) 3/24

3) QRSS

4) 2

20

-1

5) 1/8

6) 2

15

-1

7) ALL 0’S

8) 55 OCTET

(Daly)

9) ALL 1’S

55 Octet: The Daly 55 octet pattern tests circuits for line card and timing

recovery. By rapidly transitioning from a long sequence of low density octets

to high density octets, the circuit is stress tested. Following is a binary

representation of the 55 Octet stress pattern:

1000000010000000100000001000000010000000

10000000 00000001100000001000000010000000

1000000010000000100000001100000010000000

1000000010000000100000001110000010000000

10000000 10000000100000001010101010101010

1010101010101010010101010101010101010101

0101010110000000100000001000000010000000

1000000010000000111111111111111111111111

1111111111111111111111110000000110000000

0000000110000000000000011000000000000001

1000000000000001100000000000000110000000

All 1s: This pattern is composed entirely of framed ones (11111111). It

stresses circuits by maximizing power consumption.

An

Send Line Loopback Bit-Oriented Protocol (LLB BOP): This option uses FDL

loopbacks to test the T1 from the near-end toward the far-end.

1) DEACTIVATE

2) ACTIVATE

Bn

Send Payload Loopback Bit-Oriented Protocol (PLB BOP): This option uses FDL

loopbacks to test the CSU at the far-end circuit from the near-end.

1) DEACTIVATE

2) ACTIVATE

En

Reset Test Counter: This option resets the test counter to 0. The counter is

automatically reset when changing patterns.

X

Exit the T1 Port Diagnostics Menu—Returns the screen to the Diagnostics

Menu, Figure 3-16, Table 3-15.

Command

Description

Options