Verilink AS4000 (34-00244) Product Manual User Manual

Page 106

Quad Port Sync Data Module

6-6

Verilink AS4000 User Manual

More About

Loopbacks

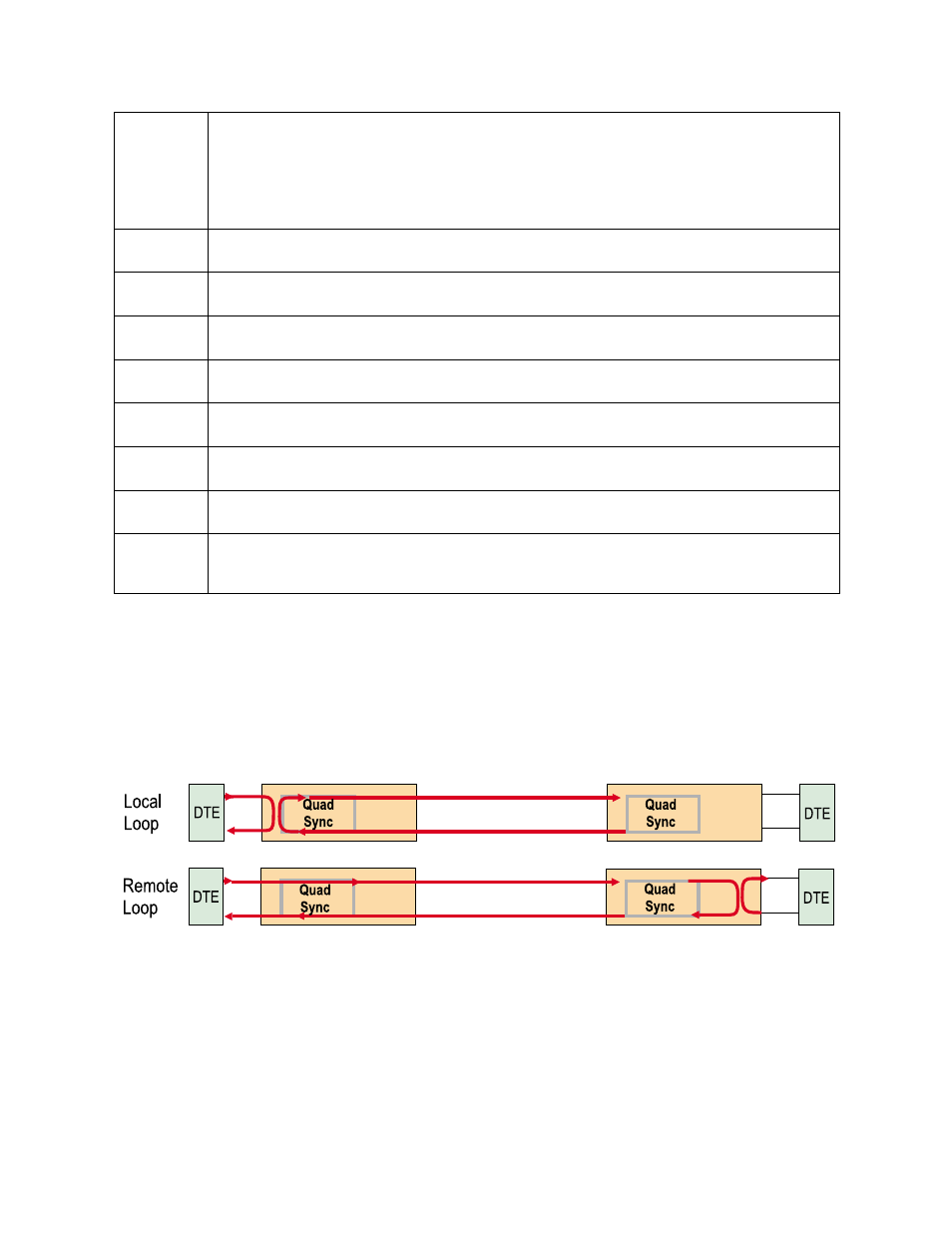

Local Loop and Remote Loop on the Quad Port Sync Data module

are both bi-directional loopbacks. If everything is working as

expected, for either loopback, the local and remote DTE should

receive its own data stream. Devices capable of detecting and

reporting a loopback should indicate either type of loop.

The data flow for local and remote loops is indicated in

.

Figure 6-6 Quad Port Sync Data Loopbacks

BERT

This is useful to test for errors on the communication circuit. The device checks for errors

by comparing a received data pattern with a known transmitted data pattern to determine

line quality.

The remote loop and data test patterns depend on interface clocks to operate. If Int/Ext or

External timing options are selected, ensure the External Clock is present and locked to the

AS4000 system clock.

Seconds in

Test

This read-only count represents the number of seconds the module was in test.

Local

Errors

This read-only count represents the number of local errored seconds that occurred while the

data module was in test.

Remote

Errors

This read-only count represents the number of remote errored seconds that occurred while

the module was in test.

TX/RX Data These fields indicate whether your Quad Port Sync Data module is transmitting or receiving

data over its serial port interface.

RTS/DCD

If RTS is On, the DTE is presenting the control lead Request To Send. If DCD is On, your

Quad Port Sync Data module is asserting Data Carrier Detect to the DTE.

DTR/DSR

If DTR is On the DTE is presenting the control lead Data Terminal Ready. If DSR is On, your

Quad Port Sync Data module is asserting Data Set Ready to the DTE.

[R]eset

counts

This command allows you to clear your counters.

Insert

[e]rrors

For test purposes, you can insert BERT errrors. This is done to verify the port is receiving its

own test pattern, rather than a test pattern from some other source in the network. It is

useful for verifying that a loopback does exist in the circuit path.