Measurement Computing CIO-QUAD0x User Manual

Page 11

4.2 CHANNEL CONTROL REGISTERS (Base + 0 through Base + 7)

The LS7266R1 contains two control registers per axis, and the configuration of each axis requires a sequence of writes to

set the operating mode of the chip. The following description outlines the configuration steps for a single axis. The first axis

control registers (channel 1) are contained at addresses BASE +0 and BASE+1. The other axis (at BASE +2 & 3, BASE +4

& 5 and BASE + 6 & 7) perform identically.

4.2.1 Base +0, 2, 4 and 6 : Output Latch and Preset Registers

When read, the BASE +0 address returns the Output Latch (OL) data. Writes to the BASE +0 address set the Preset

Register (PR). All register access to the LS7266R1 is done through byte wide operations, however, the PR and OL registers

are 24-bits wide. The LS7266R1 contains a byte pointer that is auto-incremented after each write. Setting the preset register

requires three byte-wide writes (outportb()), starting with the least significant byte. Be sure to reset the byte pointer prior to

any register writes.

4.2.2 Base +1, 3, 5 and 7: FLAG, RLD, CMR, IOR and IDR Registers

The BASE+1 address accesses the counter status when read and the control registers when written for the given axis.

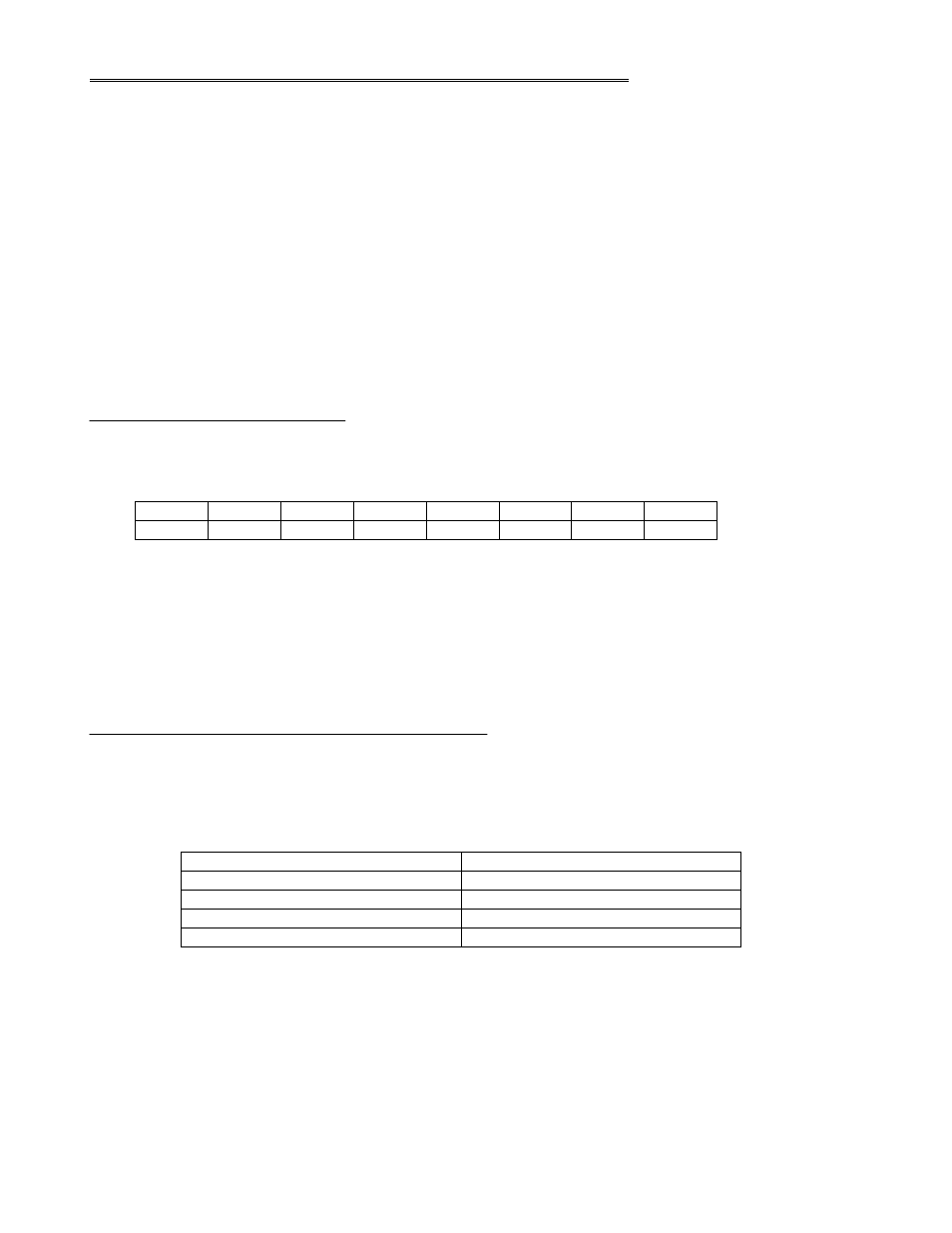

Read Counter Status (FLAG Register)

When read, the FLAG register returns the status information for the counters. The E bit of a FLAG register is set to 1 when

the noise at the quadrature inputs are wide enough to be validated by the input filter circuits. E = 1 indicates excessive noise

at the input but not a definite count error. Once set, E can only be reset via the RLD.

BT

CT

CPT

S

E

U/D

IDX

N/A

D0

D1

D2

D3

D4

D5

D6

D7

D0

BT: Borrow toggle flip-flop - toggles when CNTR underflows

D1

CT: Carry toggle flip-flop - toggles when CNTR overflows

D2

CPT: Compare toggle flip-flop - toggles when PR equals CNTR

D3

S: Sign flag - 1 when CNTR underflows, 0 when CNTR overflows

D4

E: Error flag - 1 when excessive noise at CNTR inputs in quadrature mode

D5

U/D: Up/Down flag - 1 when counting up, 0 when counting down

D6

IDX: Index - 1 when selected index input is at active level

D7

Not used - always zero

Write Counter Control (RLD, CMR, IOR & IDR Registers)

There are four unique registers which can be configured by writing to the BASE+1 register. For further details please also

refer to the LS7266R1 data sheet.

At the BASE+1 location, the four registers are uniquely selected for write access by the value in bits 5 and 6 (D5 and D6 -

see Table 4-1). The following table indicates the bit values for each register.

x11x xxxx

Index Control (IDR)

x10x xxxx

Input/Output Control (IOR)

x01x xxxx

Count Mode (CMR)

x00x xxxx

Reset and Load (RLD)

Selected for write access by bits 5 & 6

Register Name

If bit 7 (D7 - see Table 4-1) is one (1) then the selected operation will effect both the X and Y channels. If bit 7 is zero then

the X

*

/Y input is used to select the target channel. The remaining bits in each register are used to configure the LS7266R1

for various operating modes.

The following sections describe how each register can be configured. It should be noted that in several instances there are

bit fields that support multiple options. Obviously, only one option can be selected for each write operation, thus, it may be

necessary to perform several writes to the same register to achieve the desired results. For example, to initialize the RLD

register, that is, to clear all of the status flags and reset the counter, requires three separate writes to the register. Refer to the

tables below for more details.

7