D/a convert signal, D/a external time base signal – Measurement Computing PCI-DAS6023 User Manual

Page 26

PCI-DAS6023 and PCI-DAS6025 User's Guide

Functional Details

26

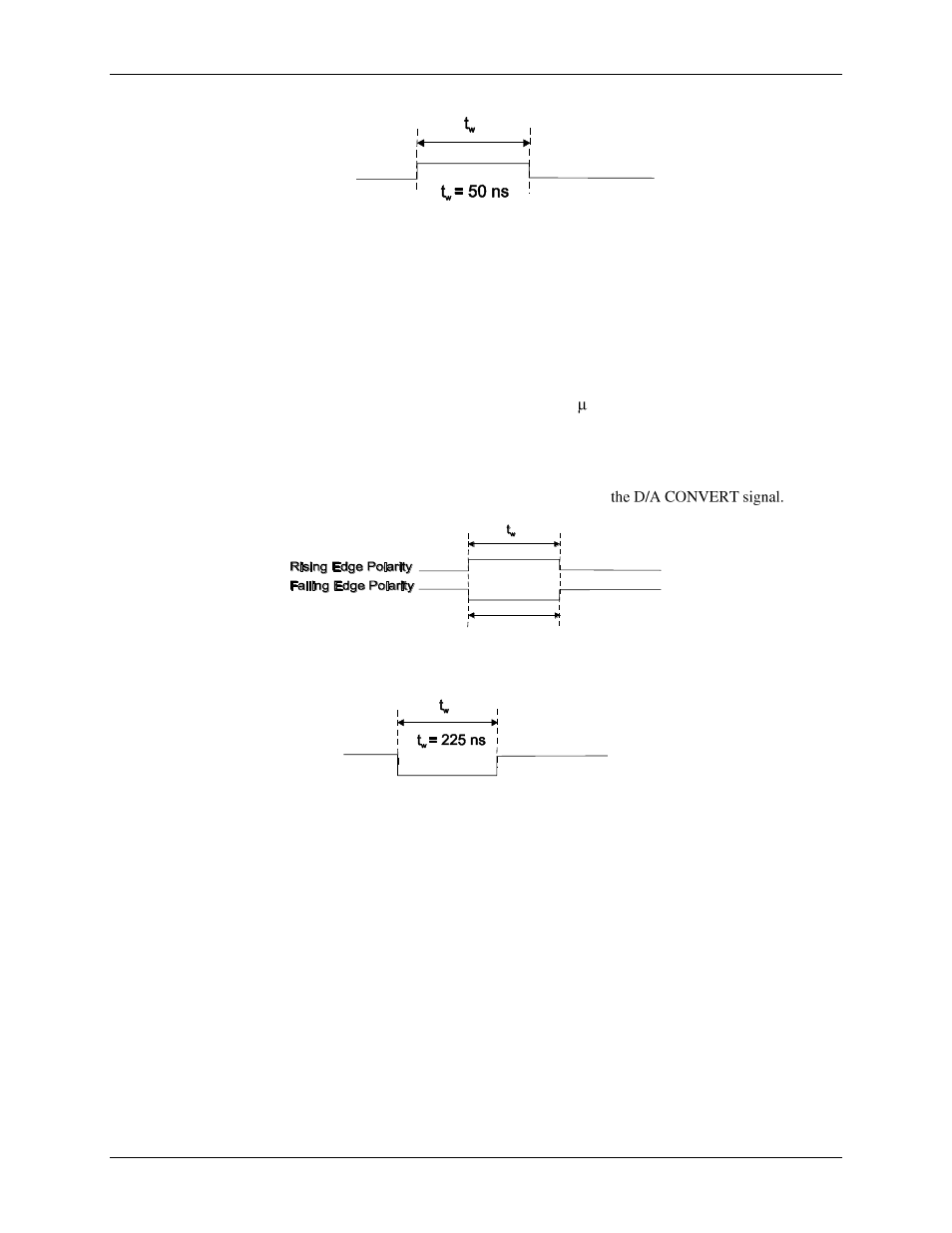

Figure 19. D/A START TRIGGER output signal timing

D/A CONVERT signal

The D/A CONVERT signal causes a single output update on the D/A converters. The DAQ-Sync ―DS D/A

UPDATE‖ input or any AUXIN pin can programmed to accept the D/A CONVERT signal. It is also available

as an output on any AUXOUT pin.

The D/A CONVERT input signal polarity is software selectable. DAC outputs will update within 100ns of the

selected edge. The D/A CONVERT pulses should be no less than 100 s apart.

When used as an output, the D/A CONVERT signal may be used to monitor the pacing of the output updates.

The output has a pulse width of 225 ns with selectable polarity.

Figure 20 and Figure 21 show the input and output timing requirements for

t

w

= 37.5 ns

minimum

Figure 20. D/A CONVERT input signal timing

Figure 21. D/A CONVERT output signal timing

D/A EXTERNAL TIME BASE signal

The D/A EXTERNAL TIME BASE signal can serve as the source for the on-board DAC pacer circuit rather

than using the internal time base. Any AUXIN pin can be set programmatically as the source for this signal. The

polarity is programmable.

The maximum frequency for the D/A EXTERNAL TIME BASE signal is 20 MHz. The minimum pulse width

is 23 ns high or low. There is no minimum frequency specification.

Figure 22 shows the timing requirements for the D/A EXTERNAL TIME BASE signal.