Daq signal timing, Scanclk signal, A/d start trigger signal – Measurement Computing PCI-DAS6023 User Manual

Page 21: E 21, Signal timing, Sect

PCI-DAS6023 and PCI-DAS6025 User's Guide

Functional Details

21

DAQ signal timing

The primary DAQ timing signals are:

SCANCLK

SSH

A/D START TRIGGER

A/D STOP TRIGGER

STARTSCAN

A/D CONVERT

A/D PACER GATE

SCANCLK signal

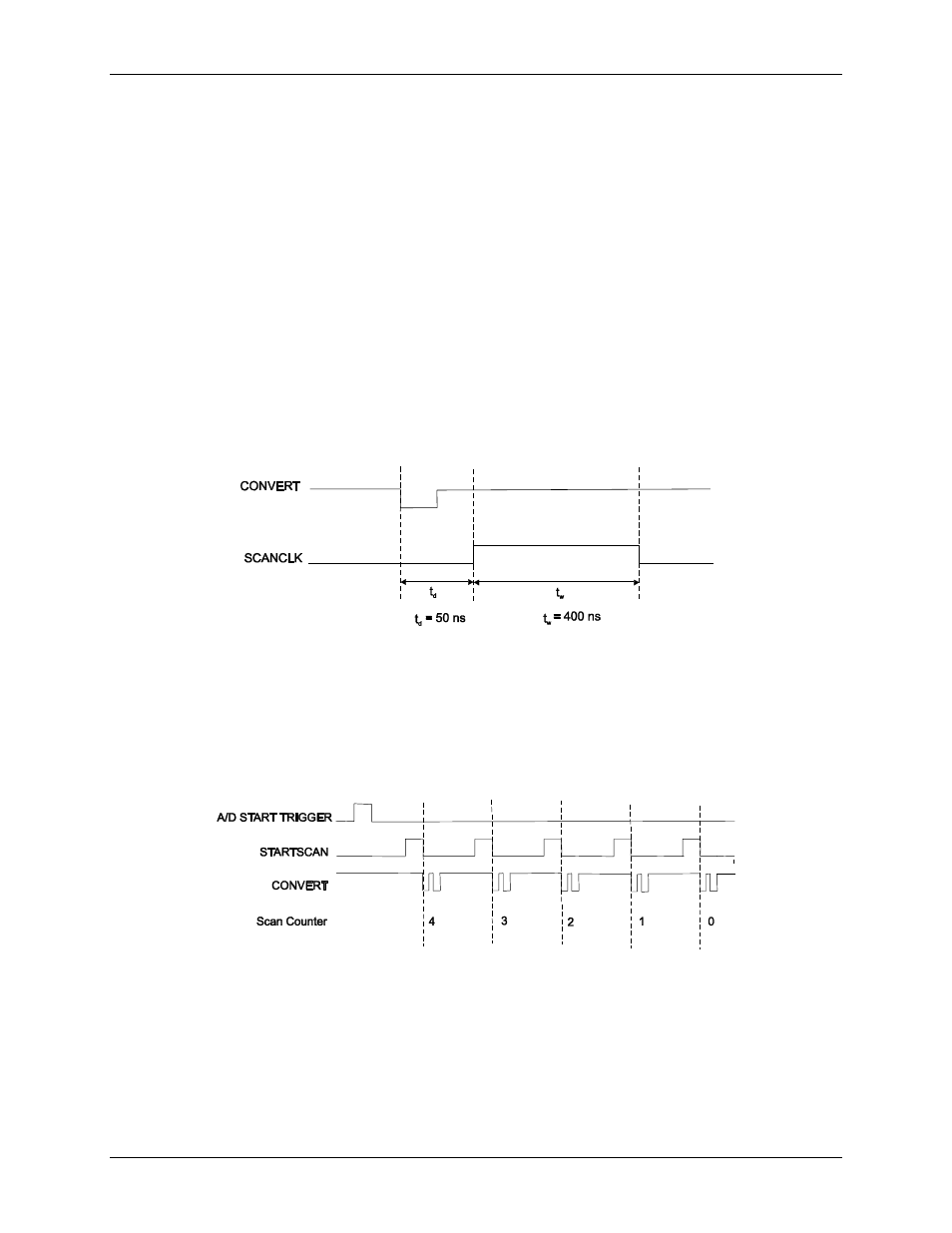

SCANCLK is an output signal that may be used for switching external multiplexers. It is a 400 ns-wide pulse

that follows the CONVERT signal after a 50 ns delay. This is adequate time for the analog input signal to be

acquired so that the next signal may be switched in. The polarity of the SCANCLK signal is programmable. The

default output pin for the SCANCLK signal is AUXOUT2, but any of the AUXOUT pins may be programmed

as a SCANCLK output.

Figure 5. SCANCLK Signal Timing

A/D START TRIGGER signal

The A/D START TRIGGER signal is used for conventional triggering, that is, when you only need to acquire

data after a trigger event. Figure 6 shows the A/D START TRIGGER signal timing for a conventionally

triggered acquisition.

Figure 6. Data Acquisition Example for Conventional Triggering

The A/D START TRIGGER source is programmable and may be set to any of the AUXIN inputs or to the

DAQ-Sync ―DS A/D START TRIGGER‖ input. The polarity of this signal is also programmable to trigger

acquisitions on either the positive or negative edge.

The A/D START TRIGGER signal is also available as an output and can be programmed to appear at any of the

AUXOUT outputs.