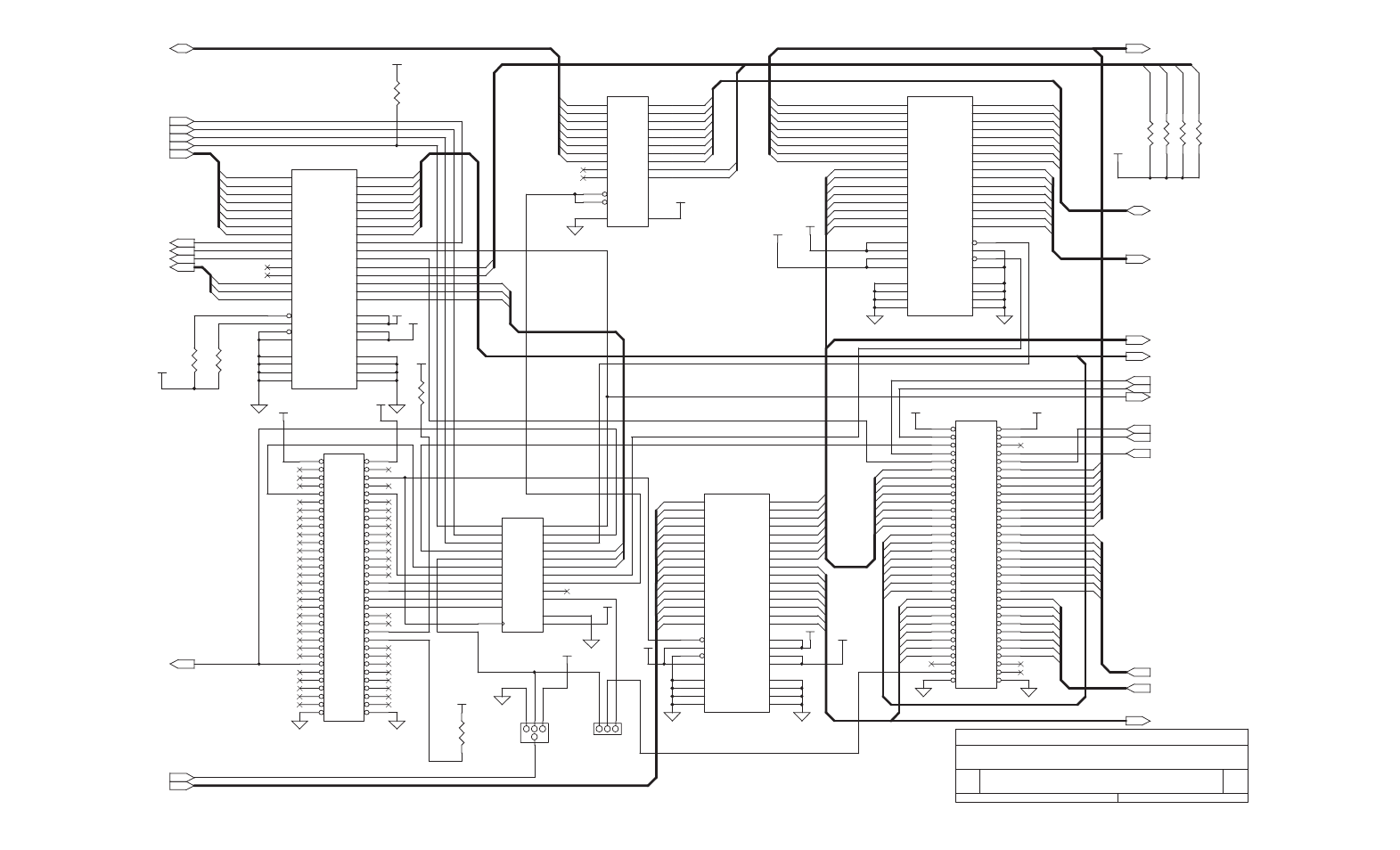

Zilog Z86C36 User Manual

Page 63

Motherboard Connection & Level Shifting

C36MISC.JED

96C0620-00 1

B

Schematic, Z86C36 Daug hter Board

B

3

4

Tuesday, July 27, 1999

Title

Size

Document Number

Rev

Date:

Sheet

of

SIZE4

nM_P25

RESET2

MA0

MA1

MA2

MA3

MA4

MA6

mUD7

MA8

MA9

MA10

MA11

MA13

MA15

U_D0

U_D1

U_D2

U_D3

U_D4

U_D5

U_D6

U_D7

mUD6

mUD4

mUD7

UD0

mUD1

mUD3

mU_P15

mUD0

mUD2

mUD2

mU_P16

mU_P17

mUD3

UD7

mU_P11

mUD0

mUD1

mUD7

mUD0

mUD2

mU_P12

mUD6

mUD1

mU_P10

mU_P10

mU_P14

mU_P15

mUD6

mUD4

mU_P13

UD1

mU_P17

mU_P16

mUD3

UD2

mU_P14

mUD5

mUD4

UD3

UD4

UD5

UD6

mU_P13

mUD5

mU_P11

mU_P12

mUD5

SIZE3

SIZE1

nRESET

ICRAM

hvC50SZ2

hvC50SZ1

hvC50SZ0

C50SZ0

C50SZ1

C50SZ2

P

u

p

1_

2

P

u

p

1_

3

SIZE2

nM_P25

RESET2

nU_M_DS

nU_RESET

nU_M_DS

hvC50SZ1

hvC50SZ0

hvC50SZ2

MA12

hvnRESET

CH_DIR

mICRAM

MA5

MA14

CH_DIR

MA7

mICRAM

hvnRESET

Pup1_6

Pup1_7

Pup1_2

Pup1_3

U_P25

U_P24

U_P23

U_P22

U_P21

U_P20

U_P27

U_P26

nU_MDS

nU_DS

mU_P26

mU_P25

mU_P24

mU_P23

mU_P22

mU_P21

mU_P20

mU_P27

mMA15

mMA14

mMA12

mMA9

mMA10

mMA8

mMA10

mMA13

mMA9

mMA13

mMA15

mMA8

mMA11

mMA11

mMA12

mMA14

mU_P07

mU_P06

mU_P05

mU_P04

mU_P03

mU_P02

mU_P01

mU_P00

mU_P37

mU_P36

mU_P35

mU_P34

mU_P33

mU_P32

mU_P31

mU_P30

mU_P27

mU_P26

mU_P25

mU_P24

mU_P23

mU_P22

mU_P21

mU_P20

mnIACK

mnU_AS

mSCLK

mnSYNC

Pup1_5

Pup1_4

P

u

p

1

_4

P

u

p

1_

5

CS_245

nCH_DIR

U_P11

U_P13

U_P15

U_P17

U_P14

U_P16

U_P10

U_P17

U_P13

U_P12

U_P10

U_P12

U_P15

U_P14

U_P11

U_P16

nCS_245

nCS_245

CS_245

BLKTGT

CH_DIR

nCH_DIR

BLKTGT

U_P34

nDM_BKOF

nDM_BKOF

nD_E

nCS_RD

nBRP_OFF

PALnBKOF

Vcc

Vcc

Vcc3_3

Vcc

Vcc

Vcc

Vcc3_3

VccICE

Vcc

Vcc

Vcc

Vcc

Vcc

Vcc3_3

Vcc

Vcc

VccICE

Vcc

Vcc

P1

Motherboard

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

64

63

P2

Motherboard

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

64

63

U14

IDT74FCT164245TPA

48

47

1

46

25

44

24

43

41

40

38

37

36

35

33

32

30

29

27

26

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

7

18

31

42

4

10

15

21

28

34

39

45

1OE

1A1

1DIR

1A2

2OE

1A3

2DIR

1A4

1A5

1A6

1A7

1A8

2A1

2A2

2A3

2A4

2A5

2A6

2A7

2A8

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

VCCB1

VCCB2

VCCA1

VCCA2

GND4

GND10

GND15

GND21

GND28

GND34

GND39

GND45

R

29

10

k

R

52

10

k

J6

1

2

3

4

R

30

10

k

R

51

10

k

R26

10K

R

42

10

k

R

41

10

k

U12

IDT74FCT164245TPA

48

47

1

46

25

44

24

43

41

40

38

37

36

35

33

32

30

29

27

26

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

7

18

31

42

4

10

15

21

28

34

39

45

1OE

1A1

1DIR

1A2

2OE

1A3

2DIR

1A4

1A5

1A6

1A7

1A8

2A1

2A2

2A3

2A4

2A5

2A6

2A7

2A8

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

VCCB1

VCCB2

VCCA1

VCCA2

GND4

GND10

GND15

GND21

GND28

GND34

GND39

GND45

J7

1

2

3

U10

QS3384

3

1

13

24

12

4

7

8

11

2

5

6

9

10

14

17

18

21

22

15

16

19

20

23

A0

nLE

nHE

VCC

GND

A1

A2

A3

A4

B0

B1

B2

B3

B4

A5

A6

A7

A8

A9

B5

B6

B7

B8

B9

R

28

10

k

R

27

10

k

U15

22V10

2

3

4

5

6

7

8

9

1

11

12

24

10

13

14

15

16

17

18

19

20

21

22

23

I2

I3

I4

I5

I6

I7

I8

I9

I/CLK

I11

Gnd

Vcc

I10

I13

IO14

IO15

IO16

IO17

IO18

IO19

IO20

IO21

IO22

IO23

U11

IDT74FCT164245TPA

48

47

1

46

25

44

24

43

41

40

38

37

36

35

33

32

30

29

27

26

2

3

5

6

8

9

11

12

13

14

16

17

19

20

22

23

7

18

31

42

4

10

15

21

28

34

39

45

1OE

1A1

1DIR

1A2

2OE

1A3

2DIR

1A4

1A5

1A6

1A7

1A8

2A1

2A2

2A3

2A4

2A5

2A6

2A7

2A8

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

VCCB1

VCCB2

VCCA1

VCCA2

GND4

GND10

GND15

GND21

GND28

GND34

GND39

GND45

MA[15..0]

<2E4

U_P1[7..0]

<>2A4

U_D[7..0]

<>2A3

nU_DS

<2E3

nU_RESET

<2A1

ICRAM

>2A3

C50SZ[2..0]

>2A4

nU_MDS

<2E3

mU_P3[7..0]<2A1

U_P2[7..0]

<2A3

mU_P0[7..0]<2A1

mnIACK

<4E3

mnU_AS

<4E3

mnSYNC

<2A1

hvnRESET

>4E3

nU_M_DS

>4E3

UD[7..0]

>2A4

mU_P2[7..0]

>4A4

mUD[7..0]

>4E2

mMA[15..8] >4E2

mU_P1[7..0] >4A4

U_P34

<1A2

CLK_VCC

<2E3

CLK_TgtVcc

2

nRESET

<>2A3;>3A3

laU_RW

< 4E3

mSCLK

<2A1

UM002202-1001 Schematic-3