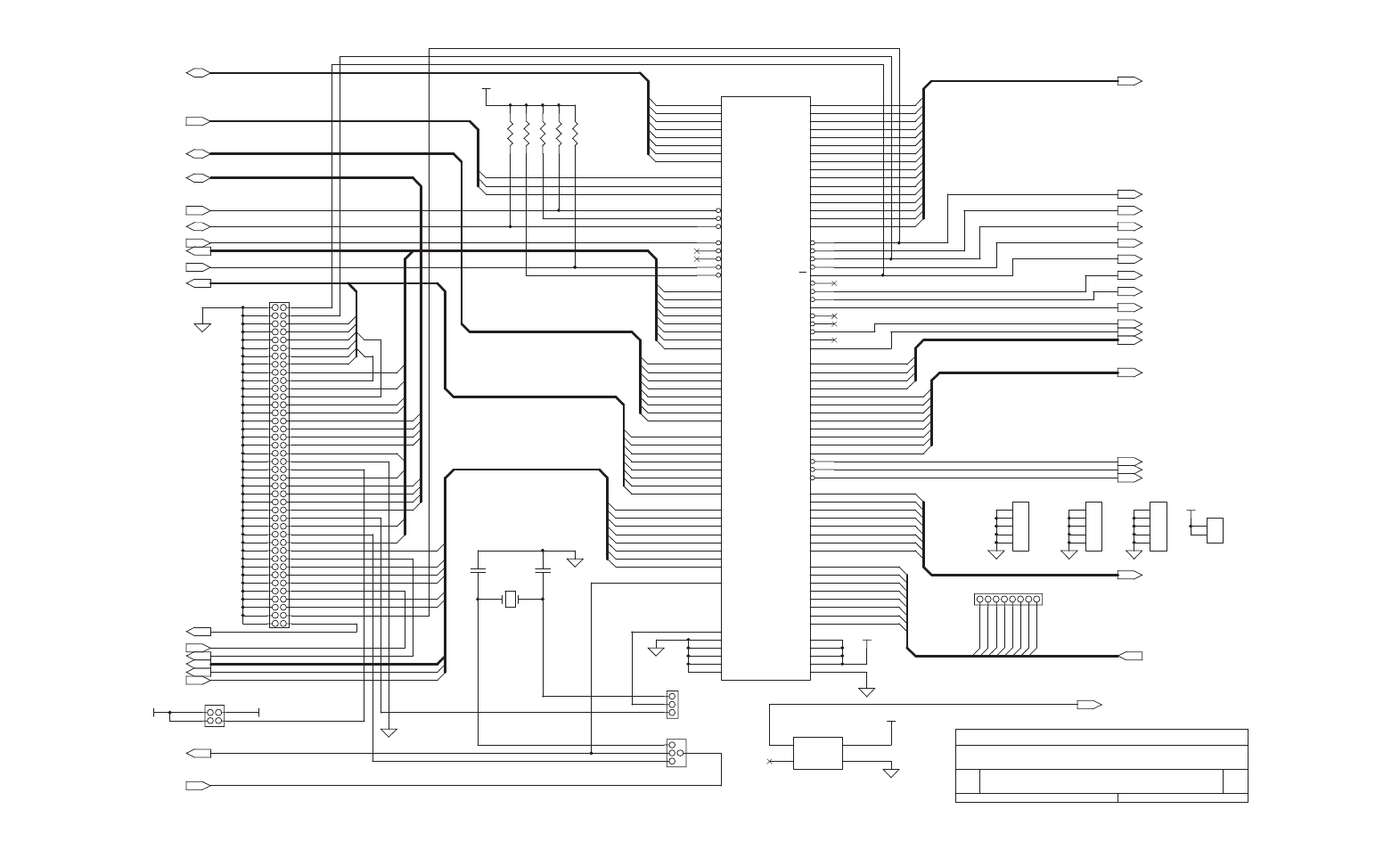

Zilog Z86C36 User Manual

Page 61

TARGET CONNECTION

ZIF SOCKET

ZIF SOCKET

ICE Chip & Target Connection

test points

96C0620-00 1

B

Schematic, Z86C36 Daug hter Board

B

1

4

Tuesday, July 27, 1999

Title

Size

Document Number

Rev

Date:

Sheet

of

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

C50SZ2

C50SZ1

C50SZ0

IWD0

IWD1

IWD2

IWD3

IWD5

IWD6

IWD7

U_P36

U_P34

U_P35

U_P37

RBP0

U_P33

RBP1

U_RW

U_P31

UD7

U_P32

RA0

U_P30

MA10

UD1

UD6

UD0

UD5

UD3

UD4

UD2

U_P05

U_P07

U_P15

U_P17

U_P11

U_P06

U_P14

U_P00

U_P03

U_P04

U_P10

U_P01

U_P16

U_P02

U_P12

U_P13

IRD5

IRD7

IRD4

IRD2

IRD3

IRD1

IRD6

IRD0

nCE_ERF

nREGWR

RA3

RA5

RA4

RA7

RA6

RA2

RA1

nREGRD

IWD4

nU_DS

nU_AS

SCLK

nSYNC

nIACK

MA8

MA9

MA11

MA12

MA13

MA14

MA15

nU_MDS

U_XTAL1

U_XTAL2

U_D2

U_D6

U_D7

U_D4

U_D5

U_D0

U_D1

U_D3

U_P36

U_P34

U_P35

nU_DS

T_P37

nU_AS

U_P25

U_P31

U_P22

U_P23

U_P27

U_P33

U_P32

U_P20

U_P26

U_P21

U_P24

VccTGT

VccTGT

U_P03

U_P06

U_P00

U_P02

U_P04

U_P05

U_P07

U_P20

U_P21

U_P22

U_P23

U_P24

U_P25

U_P26

U_P27

nIRQ3

nIRQ4

nRESET

U_RW

SMR

ADMUX

RBP2

RBP3

nU_RESET

U_P37

T_P30

U_P30

XTAL1

Crystal2

U_XTAL1

U_XTAL2

XTAL2

Crystal1

ICRAM

U_P01

nSTOP

nU_MAS

IR

D

0

IR

D

1

IR

D

2

IR

D

3

IR

D

4

IR

D

5

IR

D

6

IR

D

7

VccICE

VccADJ

VccICE

VccICE

Vcc

VccICE

TP4

CON5

1

2

3

4

5

TP3

CON5

1

2

3

4

5

TP2

CON5

1

2

3

4

5

Y1

OSC

4

2

3

1

VCC

GND

OUT

NC

TP5

CON2

1

2

J2

1

2

3

J3

1

2

3

4

R

24

10

k

J1

3

2

4

1

R

25

10

k

Y2

20MHz

C

81

22

p

F

C

80

22

p

F

TP1

1

2

3

4

5

6

7

8

R

22

10

k

R

23

10

k

P3

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

U1

Z86C50

E2

E1

F3

F2

G2

G3

G1

H1

B5

C5

B4

A3

A2

C4

B3

A1

B8

A8

B7

C7

A6

B6

C6

A5

C3

B2

B1

D3

C2

C1

D2

D1

J3

M8

N8

L7

M7

N6

M6

L6

N5

M5

N4

M4

N3

M3

L4

N2

M2

L1

K2

K3

K4

D4

K1

D10

L2

N1

L3

L5

H2

J1

J2

M1

L8

N11

M9

M10

L9

N12

L10

M11

N13

K10

L11

M12

M13

K11

L12

L13

K12

J11

K13

J12

C11

B12

A12

C10

B11

A11

B10

C9

A10

B9

A9

C8

N10

E3

D13

A4

A7

J13

N9

F1

H11

H12

H13

G12

G11

G13

F13

F12

E13

E12

E11

D12

C13

B13

D11

C12

H3

N7

F11

A13

P10

P11

P12

P13

P14

P15

P16

P17

P20

P21

P22

P23

P24

P25

P26

P27

P00

P01

P02

P03

P04

P05

P06

P07

P30

P31

P32

P33

P34

P35

P36

P37

R/W

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

AS

DS

SYNC

WAIT

HALT

HOLD

STOP

IACK

MAS

MDS

SMR

DM

RESET

DTIMERS

SCLK

ADMUX

XTAL1

XTAL2

IRQ3

IRQ4

RBP0

RBP1

RBP2

RBP3

SCLKN

IWD0

IWD1

IWD2

IWD3

IWD4

IWD5

IWD6

IWD7

REGWR

REGRD

CE_ERF

D0

D1

D2

D3

D4

D5

D6

D7

SIZE0

SIZE1

SIZE2

VCC_N10

VCC_E3

VCC_D13

VCC_A4

GND_A7

GND_J13

GND_N9

GND_F1

RA0

RA1

RA2

RA3

RA4

RA5

RA6

RA7

IRD0

IRD1

IRD2

IRD3

IRD4

IRD5

IRD6

IRD7

GND_H3

GND_N7

CT0

TCLK

R

21

10

k

nIRQ3

<3A1

SMR

<3A3

nRESET

<1E4;>3A3

T_P37

<3A1

C50SZ[2..0]

<1A3

UD[7..0]

<>1E3

MA[15..0]

>1A1

nSTOP

>3A3

nSYNC

>1A4

nIACK

>1A4

nU_AS

>4E4

nU_RESET

>1A4

U_P1[7..0]

<>1E4

XTAL1

>3A3

T_P30

>3A2

U_P37

>3A2

IRD[7..0]

<3A4

IWD[7..0]

>3A4

RBP[3..0]

>3A4,>4A1

RA[7..0]

>3A4,>4A3

nREGRD

>3A4

nREGWR

>3A4

nCE_ERF >3A4

SCLK

>1A4;>3A3

U_D[7..0]

<>1A4

nU_DS

>1A4

nU_MDS

>1A4

U_RW

>1A4

U_P30

<3A1

U_P2[7..0]

>1A4

ICRAM

<1E4

U_P0[7..0]

>1E1

U_P3[7..0]

>1E1

TCLK

>4E4

nU_MAS

>4E4

CLK_VCC

>1

CLK_TgtVcc

1

UM002202-1001 Schematic-1