Altera Data Conversion HSMC User Manual

Page 35

Appendix B: Pin-Out Information for the Stratix III (3SL150) Development Board

B–3

© November 2008

Altera Corporation

Data Conversion HSMC Reference Manual

provides the HSMC Port B interface pin-out information for the Stratix III

(3SL150) development board.

138

LVDS RX or CMOS I/O bit 14

DB1

HSMA_RX_P14

LVDS or 2.5 V

AC4

139

LVDS TX or CMOS I/O bit 14

DA0

HSMA_TX_N14

LVDS or 2.5 V

Y9

140

LVDS RX or CMOS I/O bit 14

DB0

HSMA_RX_N14

LVDS or 2.5 V

AB3

143

LVDS TX or CMOS I/O bit 15

AIC_DIN

HSMA_TX_P15

LVDS or 2.5 V

W12

144

LVDS RX or CMOS I/O bit 15

AIC_DOUT

HSMA_RX_P15

LVDS or 2.5 V

AB4

145

LVDS TX or CMOS I/O bit 15

AIC_LRCIN

HSMA_TX_N15

LVDS or 2.5 V

Y11

146

LVDS RX or CMOS I/O bit 15

AIC_LRCOUT

HSMA_RX_N15

LVDS or 2.5 V

AA3

149

LVDS TX or CMOS I/O bit 16

AIC_BCLK

HSMA_TX_P16

LVDS or 2.5 V

AA12

150

LVDS RX or CMOS I/O bit 16

AIC_XCLK

HSMA_RX_P16

LVDS or 2.5 V

AA4

151

LVDS TX or CMOS I/O bit 16

AIC_SPI_CS

HSMA_TX_N16

LVDS or 2.5 V

AB11

155

LVDS or CMOS clock out

FPGA_CLK_B_P

HSMA_CLK_OUT_P2

LVDS

W8

156

LVDS or CMOS clock in

ADA_DCO

HSMA_CLK_IN_P2

LVDS

T2

157

LVDS or CMOS clock out

FPGA_CLK_B_N

HSMA_CLK_OUT_N2

2.5 V

W7

158

LVDS or CMOS clock in

ADB_DCO

HSMA_CLK_IN_N2

2.5 V

T1

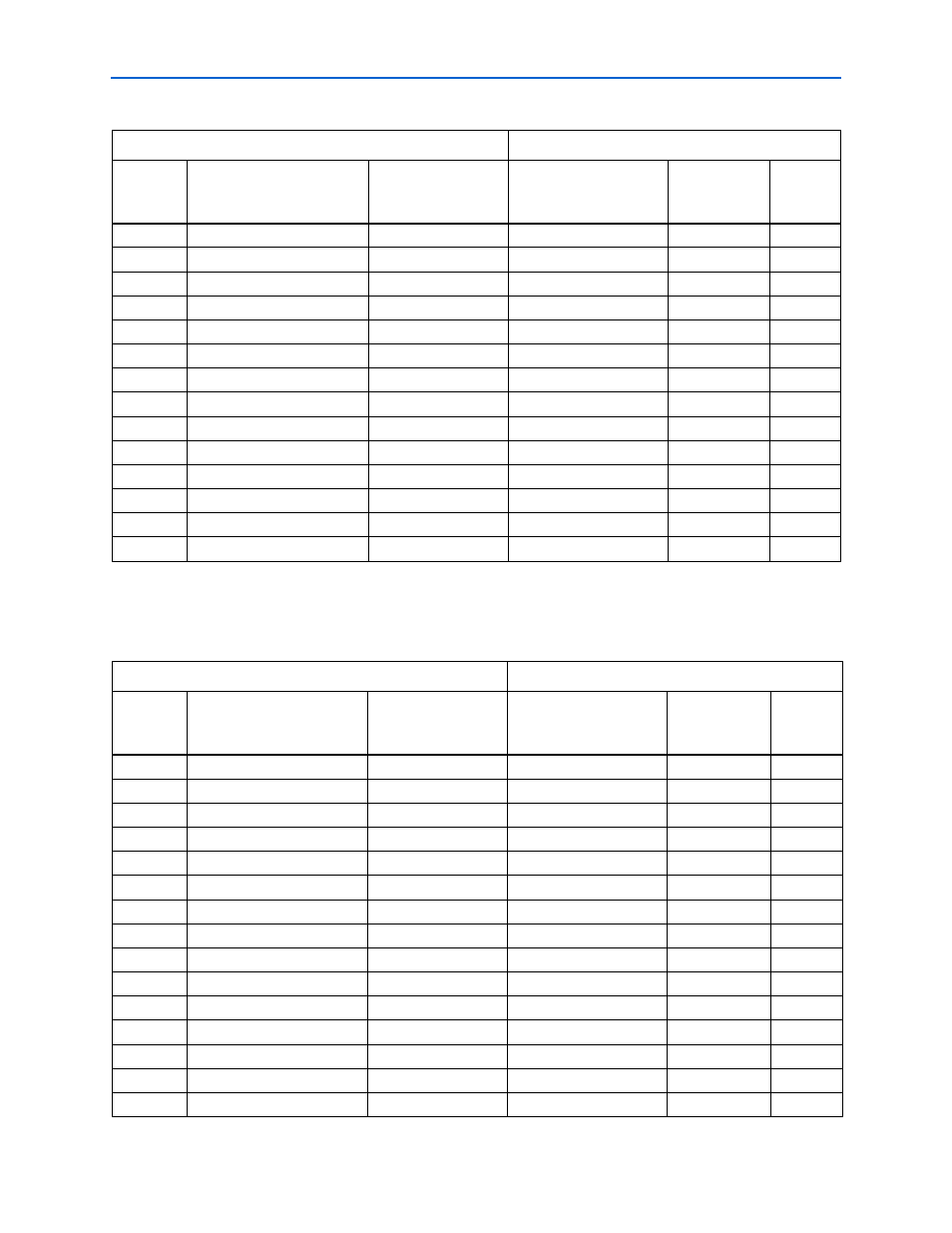

Table B–1. HSMC Port A Interface Pin-Out Information (Part 3 of 3)

Data Conversion HSMC Schematic

Development Board Schematic

Board

Reference

(J1)

Description

Schematic

Signal Name

Schematic

Signal Name

I/O Standard

Stratix III

Pin

Number

Table B–2. HSMC Port B Interface Pin-Out Information (Part 1 of 3)

Data Conversion HSMC Schematic

Development Board Schematic

Board

Reference

(J1)

Description

Schematic

Signal Name

Schematic

Signal Name

I/O Standard

Stratix III

Pin

Number

33

Serial data

SDA

HSMB_SDA

2.5 V

U11

34

Serial clock

SCL

HSMB_SCL

2.5 V

AD31

41

Dedicated CMOS I/O bit 0

ADA_D13

HSMB_D0

2.5 V

AB24

42

Dedicated CMOS I/O bit 1

ADB_D13

HSMB_D1

2.5 V

AB25

43

Dedicated CMOS I/O bit 2

ADA_D12

HSMB_D2

2.5 V

AF32

44

Dedicated CMOS I/O bit 3

ADB_D12

HSMB_D3

2.5 V

AF31

47

LVDS TX or CMOS I/O bit 0

ADA_D11

HSMB_TX_P0

LVDS or 2.5 V

P11

48

LVDS RX or CMOS I/O bit 0

ADB_D11

HSMB_RX_P0

LVDS or 2.5 V

R4

49

LVDS TX or CMOS I/O bit 0

ADA_D10

HSMB_TX_N0

LVDS or 2.5 V

P10

50

LVDS RX or CMOS I/O bit 0

ADB_D10

HSMB_RX_N0

LVDS or 2.5 V

R3

53

LVDS TX or CMOS I/O bit 1

ADA_D9

HSMB_TX_P1

LVDS or 2.5 V

T9

54

LVDS RX or CMOS I/O bit 1

ADB_D9

HSMB_RX_P1

LVDS or 2.5 V

P4

55

LVDS TX or CMOS I/O bit 1

ADA_D8

HSMB_TX_N1

LVDS or 2.5 V

T8

56

LVDS RX or CMOS I/O bit 1

ADB_D8

HSMB_RX_N1

LVDS or 2.5 V

P3

59

LVDS TX or CMOS I/O bit 2

ADA_D7

HSMB_TX_P2

LVDS or 2.5 V

T7