Altera Data Conversion HSMC User Manual

Page 27

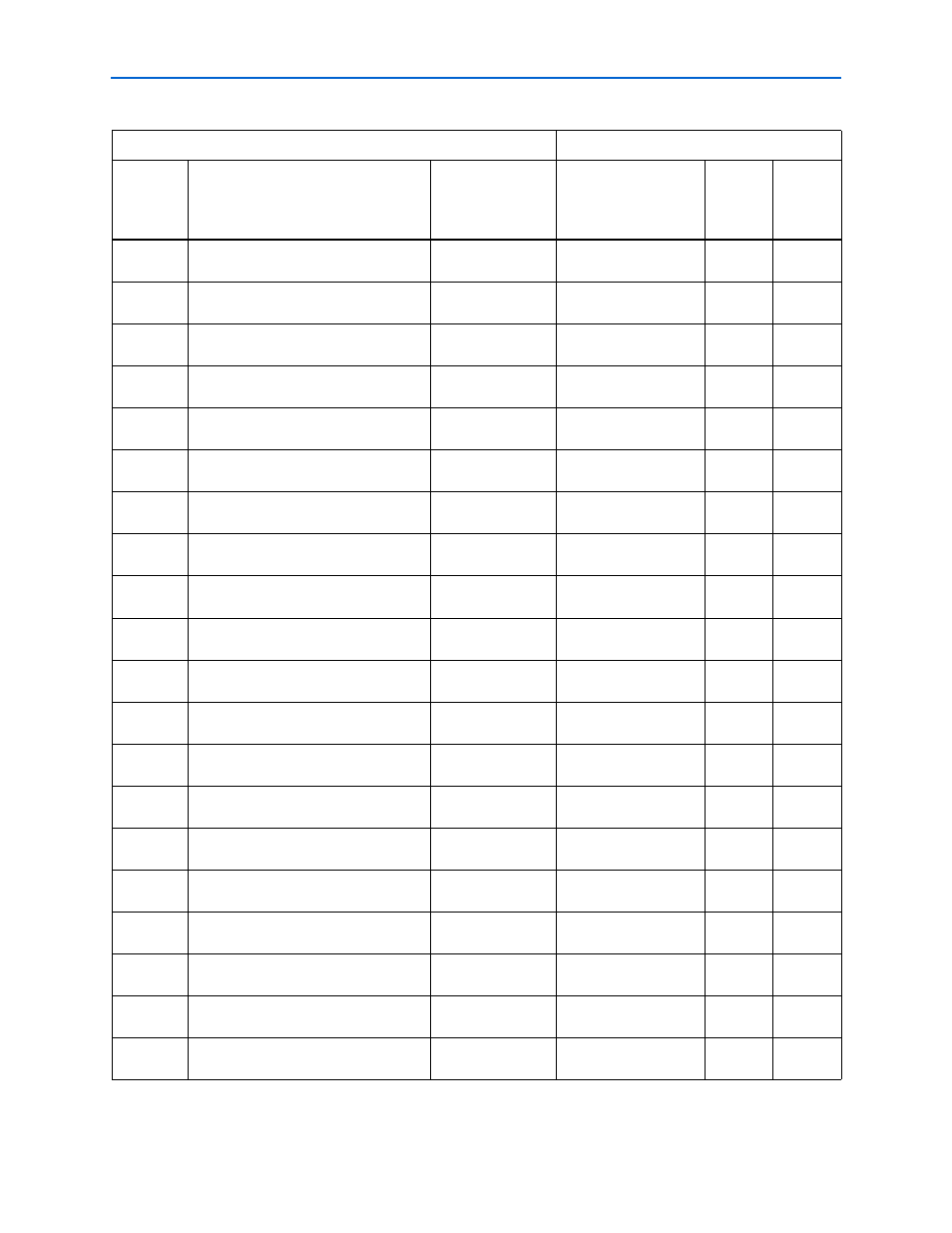

Appendix A: Pin-Out Information for the Cyclone III (3C120) Development Board

A–3

© November 2008

Altera Corporation

Data Conversion HSMC Reference Manual

96

LVDS or CMOS clock in

XT_IN_P

HSMA_CLK_IN_P1

LVDS or

2.5 V

Y2

97

LVDS or CMOS clock out

FPGA_CLK_A_N

HSMA_CLK_OUT_N1

LVDS or

2.5 V

G5

98

LVDS or CMOS clock in

XT_IN_N

HSMA_CLK_IN_N1

LVDS or

2.5 V

Y1

101

LVDS TX 8p or CMOS I/O data bit 40

DA13

HSMA_TX_D_P8

LVDS or

2.5 V

L7

102

LVDS RX 8p or CMOS I/O data bit 41

DB13

HSMA_RX_D_P8

LVDS or

2.5 V

N4

103

LVDS TX 8n or CMOS I/O data bit 42

DA12

HSMA_TX_D_N8

LVDS or

2.5 V

L6

104

LVDS RX 8n or CMOS I/O data bit 43

DB12

HSMA_RX_D_N8

LVDS or

2.5 V

N3

107

LVDS TX 9p or CMOS I/O data bit 44

DA11

HSMA_TX_D_P9

LVDS or

2.5 V

K8

108

LVDS RX 9p or CMOS I/O data bit 45

DB11

HSMA_RX_D_P9

LVDS or

2.5 V

L4

109

LVDS TX 9n or CMOS I/O data bit 46

DA10

HSMA_TX_D_N9

LVDS or

2.5 V

L8

110

LVDS RX 9n or CMOS I/O data bit 47

DB10

HSMA_RX_D_N9

LVDS or

2.5 V

L3

113

LVDS TX 10p or CMOS I/O data bit 48

DA9

HSMA_TX_D_P10

LVDS or

2.5 V

K4

114

LVDS RX 10p or CMOS I/O data bit 49

DB9

HSMA_RX_D_P10

LVDS or

2.5 V

L2

115

LVDS TX 10n or CMOS I/O data bit 50

DA8

HSMA_TX_D_N10

LVDS or

2.5 V

K3

116

LVDS RX 10n or CMOS I/O data bit 51

DB8

HSMA_RX_D_N10

LVDS or

2.5 V

L1

119

LVDS TX 11p or CMOS I/O data bit 52

DA7

HSMA_TX_D_P11

LVDS or

2.5 V

J4

120

LVDS RX 11p or CMOS I/O data bit 53

DB7

HSMA_RX_D_P11

LVDS or

2.5 V

K2

121

LVDS TX 11n or CMOS I/O data bit 54

DA6

HSMA_TX_D_N11

LVDS or

2.5 V

J3

122

LVDS RX 11n or CMOS I/O data bit 55

DB6

HSMA_RX_D_N11

LVDS or

2.5 V

K1

125

LVDS TX 12p or CMOS I/O data bit 56

DA5

HSMA_TX_D_P12

LVDS or

2.5 V

J7

Table A–1. HSMC Port A Interface Pin-Out Information (Part 3 of 4)

Data Conversion HSMC Schematic

Development Board Schematic

Board

Reference

(J1)

Description

Schematic

Signal Name

Schematic

Signal Name

I/O

Standard

Cyclone

III

Pin

Number