Figure 2–5 – Altera Data Conversion HSMC User Manual

Page 16

2–10

Chapter 2: Board Components and Interfaces

Component Interfaces

Data Conversion HSMC Reference Manual

© November 2008

Altera Corporation

provides the differential to LVDS clock multiplexer pin-out details.

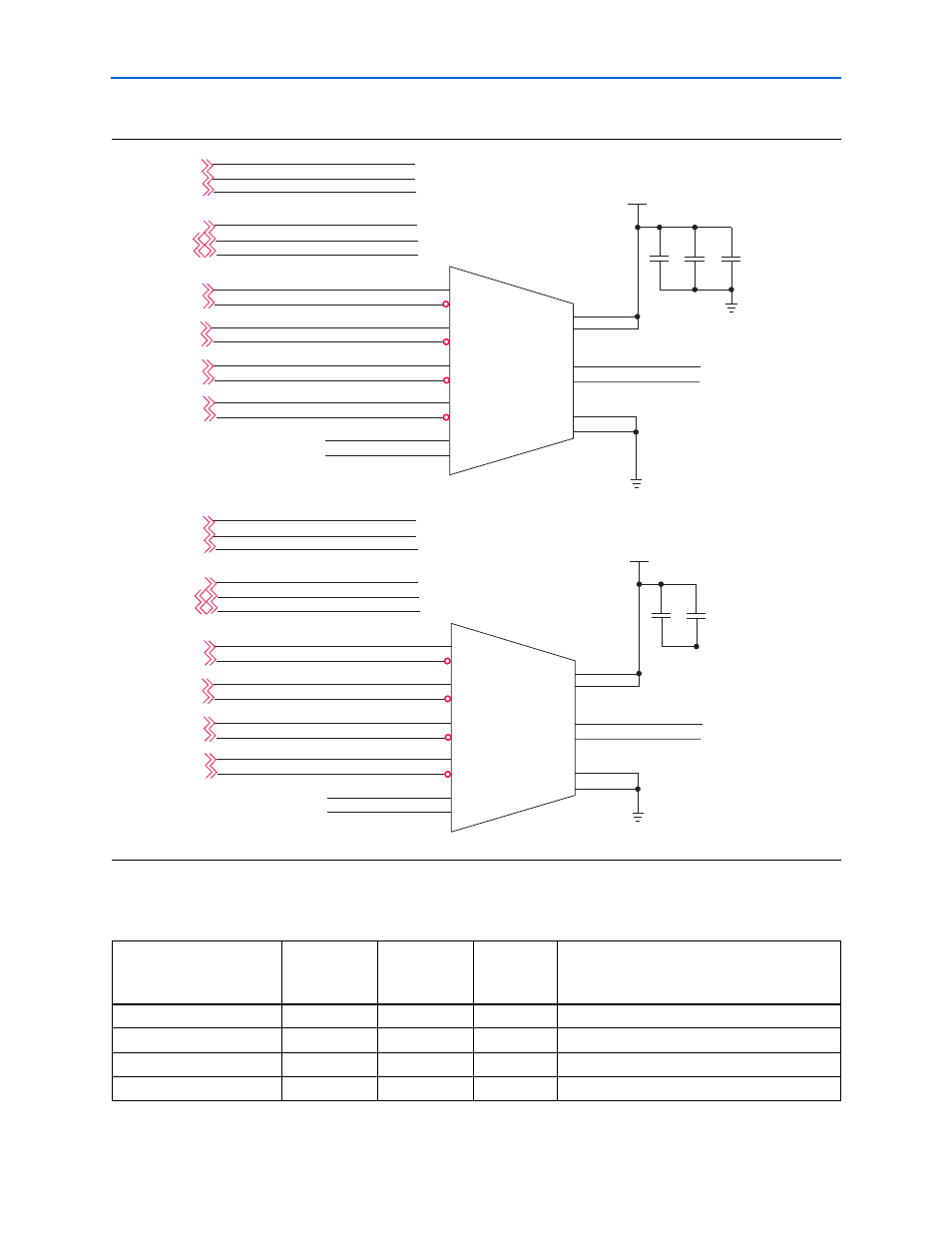

Figure 2–5. A/D Converter Clocking Options

ADA_OE

ADA_CLK_P

ADA_CLK_N

ADA_OE

ADA_CLK_N

ADA_CLK_P

ADA_SPI_CS

ADA_SDIO

ADA_ACLK

FPGA_CLK_A_P

NO_CLK_P

NO_CLK_N

ADA_CLK_S1

ADA_CLK_S0

PCLK0P

PCLK0N

PCLK1P

PCLK1N

PCLK2P

PCLK2N

PCLK3P

PCLK3N

SEL0

SEL1

VDD

VDD

QP

QN

GND

GND

3.3 V

ADA_CLK_SEL_N

ADA_CLK_SEL_P

ADA_SPI_CS

ADA_SDIO

ADA_SCLK

FPGA_CLK_A_N

FPGA_CLK_A_P

FPGA_CLK_A_N

1

2

3

4

FPGA_CLK_B_P

FPGA_CLK_B_N

FPGA_CLK_B_P

FPGA_CLK_B_N

XT_IN_P

XT_IN_N

XT_IN_P

XT_IN_N

9

10

11

12

NO_CLK_P

NO_CLK_N

6

7

13

8

15

14

5

16

C98

C99

C100

10µF

0.1µF 1.0nF

ICS854054

U9

ADB_OE

ADB_CLK_P

ADB_CLK_N

ADB_OE

ADB_CLK_N

ADB_CLK_P

ADB_SPI_CS

AD_SDIO

AD_SCLK

FPGA_CLK_A_P

NO_CLK_P

NO_CLK_N

ADB_CLK_S1

ADB_CLK_S0

PCLK0P

PCLK0N

PCLK1P

PCLK1N

PCLK2P

PCLK2N

PCLK3P

PCLK3N

SEL0

SEL1

VDD

VDD

QP

QN

GND

GND

3.3 V

ADB_CLK_SEL_N

ADB_CLK_SEL_P

ADB_SPI_CS

AD_SDIO

AD_SCLK

FPGA_CLK_A_N

FPGA_CLK_A_P

FPGA_CLK_A_N

1

2

3

4

FPGA_CLK_B_P

FPGA_CLK_B_N

FPGA_CLK_B_P

FPGA_CLK_B_N

XT_IN_P

XT_IN_N

XT_IN_P

XT_IN_N

9

10

11

12

NO_CLK_P

NO_CLK_N

6

7

13

8

15

14

5

16

C101 C102

1.0nF

0.1µF

ICS854054

U10

Table 2–12. Differential to LVDS Clock Multiplexer (U9, U10) Pin-Out Information (Part 1 of 2)

Schematic Signal

HSMC

Connector

Pin Number

Device Signal

Device Pin

Number

Description

FPGA_CLK_A_P

95

PCLK0P

1

Non-inverting Differential clock input

FPGA_CLK_A_N

97

PCLK0N

2

Inverting Differential clock input

FPGA_CLK_B_P

155

PCLK1P

3

Non-inverting Differential clock input

FPGA_CLK_B_N

157

PCLK1N

4

Inverting Differential clock input