A. programming the flash device, Board update portal cfi flash memory map, Appendix a. programming the flash device – Altera Transceiver Signal Integrity User Manual

Page 23

December 2014

Altera Corporation

Transceiver Signal Integrity Development Kit,

Stratix IV GT Edition User Guide

A. Programming the Flash Device

There is a common flash interface (CFI) type flash memory device on the Stratix IV GT

transceiver signal integrity board. When you first receive the kit, the CFI flash device

arrives programmed with a default factory FPGA configuration for running the Board

Update Portal example design and a default user configuration for running the

primary transceiver signal integrity demonstration. There are several other factory

software files written to the CFI flash device to support the running of the Board

Update Portal. These software files were created using the Nios II EDS just as the

hardware design was created using the Quartus II Design application.

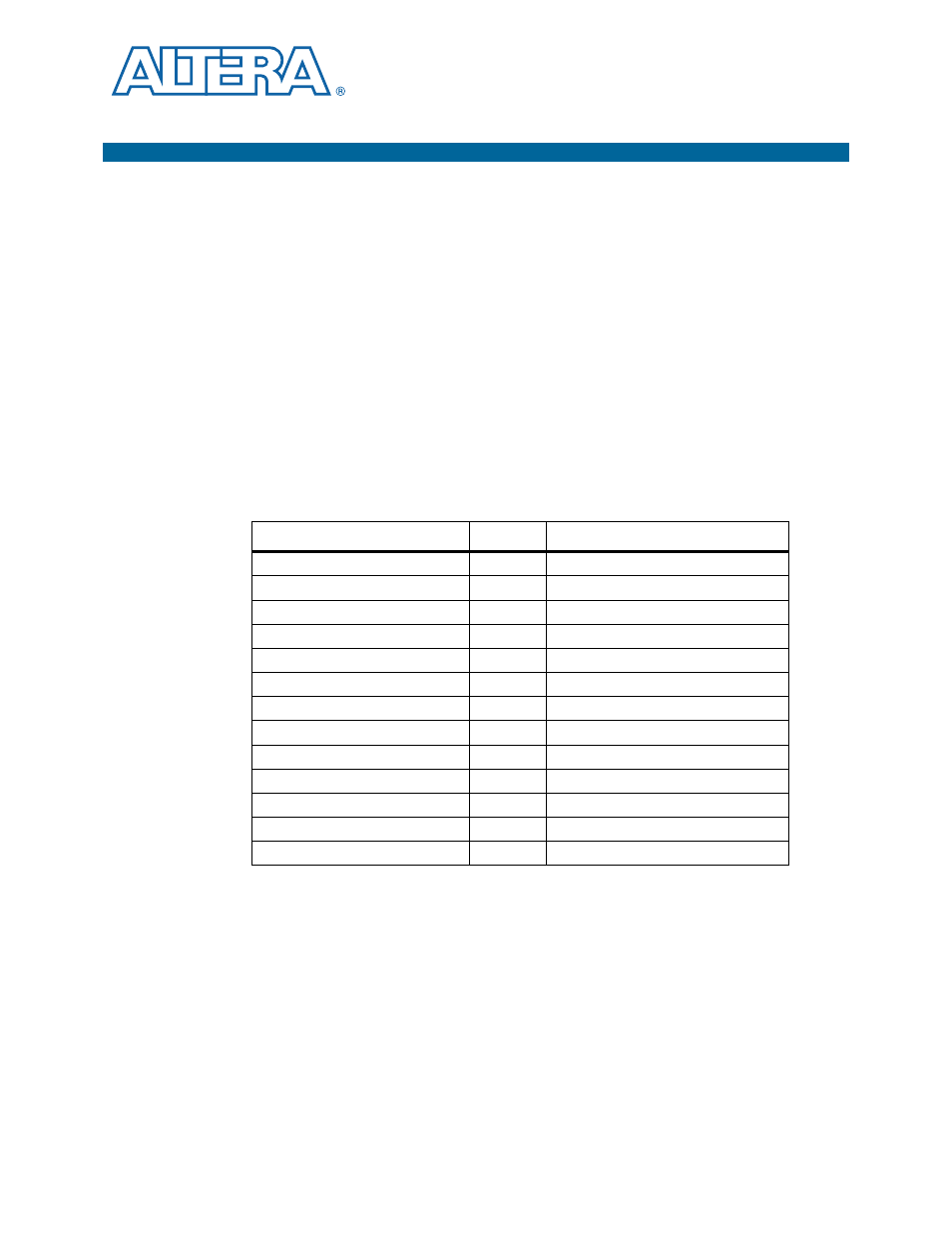

Board Update Portal CFI Flash Memory Map

shows the default memory contents of the 512-Mb (64-MB) single-die CFI

flash device. For the Board Update Portal to run correctly and update designs in the

user memory, this memory map must not be altered.

Using the Board Update Portal or Nios II EDS tools, you can update the user flash

configuration with designs provided on Altera’s website for demonstration and

evaluation. For more information, refer to

“Board Update Portal” on page 5–1

c

Altera advises against overwriting the FACTORY HW or SW images unless you are

expert with the Altera tools or overwriting the factory design is deliberate. If you

unintentionally overwrite the FACTORY HW or SW images, refer to

Factory Design to the Flash Device” on page A–4

.

Table A–1. Byte Address Flash Memory Map

Block Description

Size

Address Range

Unused

32 KB

0x03FF8000 - 0x03FFFFFF

Unused

32 KB

0x03FF0000 - 0x03FF7FFF

Unused

32 KB

0x03FE8000 - 0x03FEFFFF

Unused

32 KB

0x03FE0000 - 0x03FE7FFF

User software

24,320 KB

0x02820000 - 0x03FDFFFF

Factory software

8,192 KB

0x02020000 - 0x0281FFFF

zipfs (html, web content)

8,192 KB

0x01820000 - 0x0201FFFF

User hardware

12,288 KB

0x00C20000 - 0x0181FFFF

Factory hardware

12,288 KB

0x00020000 - 0x00C1FFFF

PFL option bits

32 KB

0x00018000 - 0x0001FFFF

Reserved

32 KB

0x00010000 - 0x00017FFF

Ethernet option bits

32 KB

0x00008000 - 0x0000FFFF

User design reset vector

32 KB

0x00000000 - 0x00007FFF