Extended custom instructions, Extended custom instructions –7 – Altera Nios II Custom User Manual

Page 11

Chapter 1: Nios II Custom Instruction Overview

1–7

Custom Instruction Types

January 2011

Altera Corporation

Nios II Custom Instruction User Guide

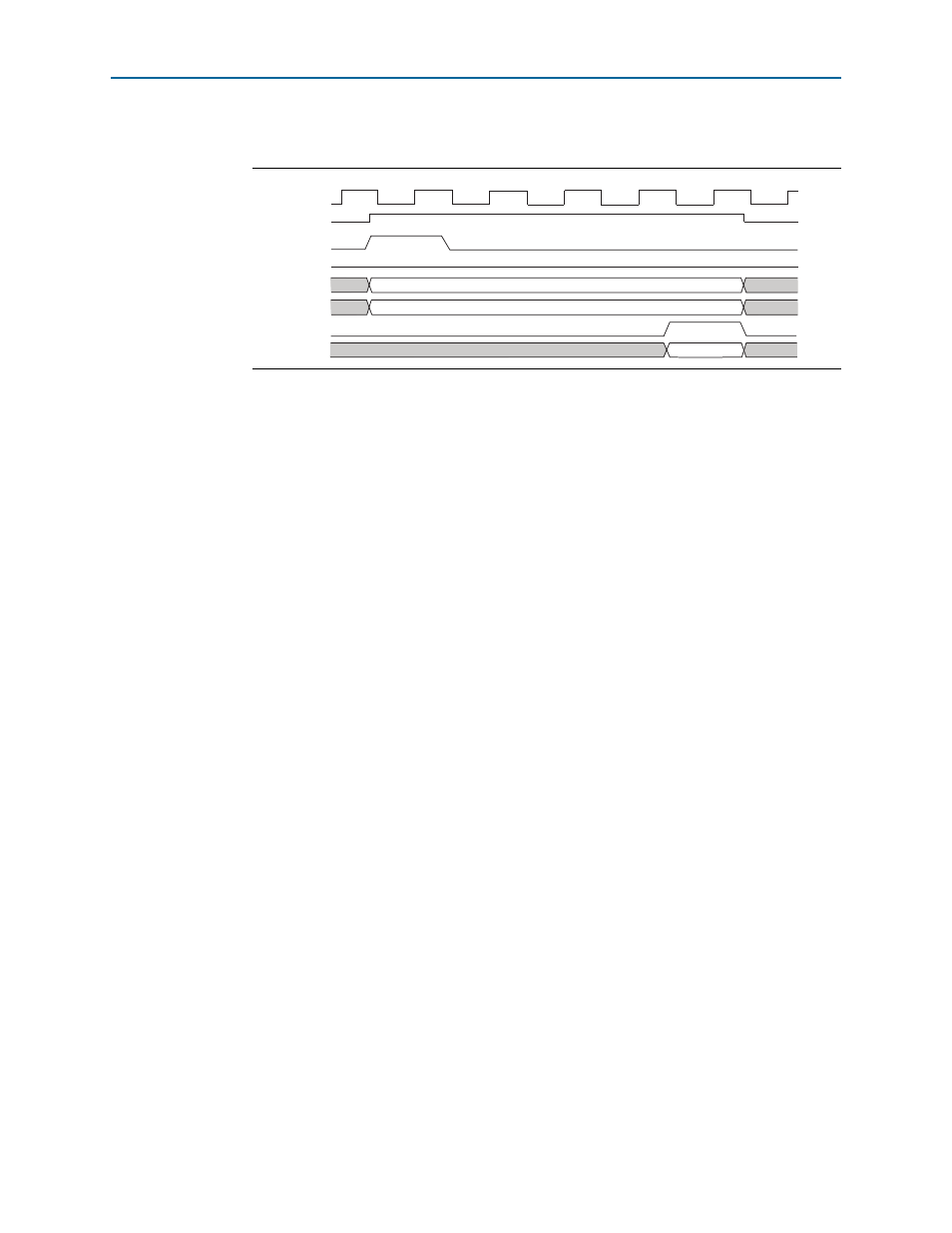

shows the multicycle custom instruction hardware port timing diagram.

The processor asserts the active high

start

port on the first clock cycle of the custom

instruction execution. At this time, the

dataa

and

datab

ports have valid values and

remain valid throughout the duration of the custom instruction execution. The

start

signal is asserted for a single clock cycle.

For a fixed length multicycle custom instruction, after the instruction starts, the

processor waits the specified number of clock cycles, and then reads the value on the

result

signal. For an n-cycle operation, the custom logic block must present valid

data on the n

th

rising edge after the custom instruction begins execution.

For a variable length multicycle custom instruction, the processor waits until the

active high

done

signal is asserted. The processor reads the

result

port on the same

clock edge on which

done

is asserted. The custom logic block must present data on the

result

port on the same clock cycle on which it asserts the

done

signal.

The Nios II system clock feeds the custom logic block’s

clk

port, and the Nios II

system’s master reset feeds the active high

reset

port. The

reset

port is asserted only

when the whole Nios II system is reset.

The custom logic block must treat the active high

clk_en

port as a conventional clock

qualifier signal, ignoring

clk

while

clk_en

is deasserted.

You can further optimize multicycle custom instructions by implementing the

extended internal register file, or by creating external interface custom instructions.

Refer to

“Extended Custom Instructions”

,

“Internal Register File Custom

, or

“External Interface Custom Instructions” on page 1–10

.

Extended Custom Instructions

Extended custom instruction allows a single custom logic block to implement several

different operations. Extended custom instructions use an index to specify which

operation the logic block performs. The index can be as many as eight bits wide,

allowing a single custom logic block to implement as many as 256 different

operations.

Figure 1–6. Multicycle Custom Instruction Timing Diagram

clk

dataa[]

datab[]

result[]

valid

valid

T0

T1

T3

T2

T4

T5

T6

valid

done

clk_en

start

reset