Altera MAX II User Manual

Page 27

Altera Corporation

Development Kit Version 1.1.0

2–19

July 2005

MAX II Development Kit Getting Started User Guide

Getting Started

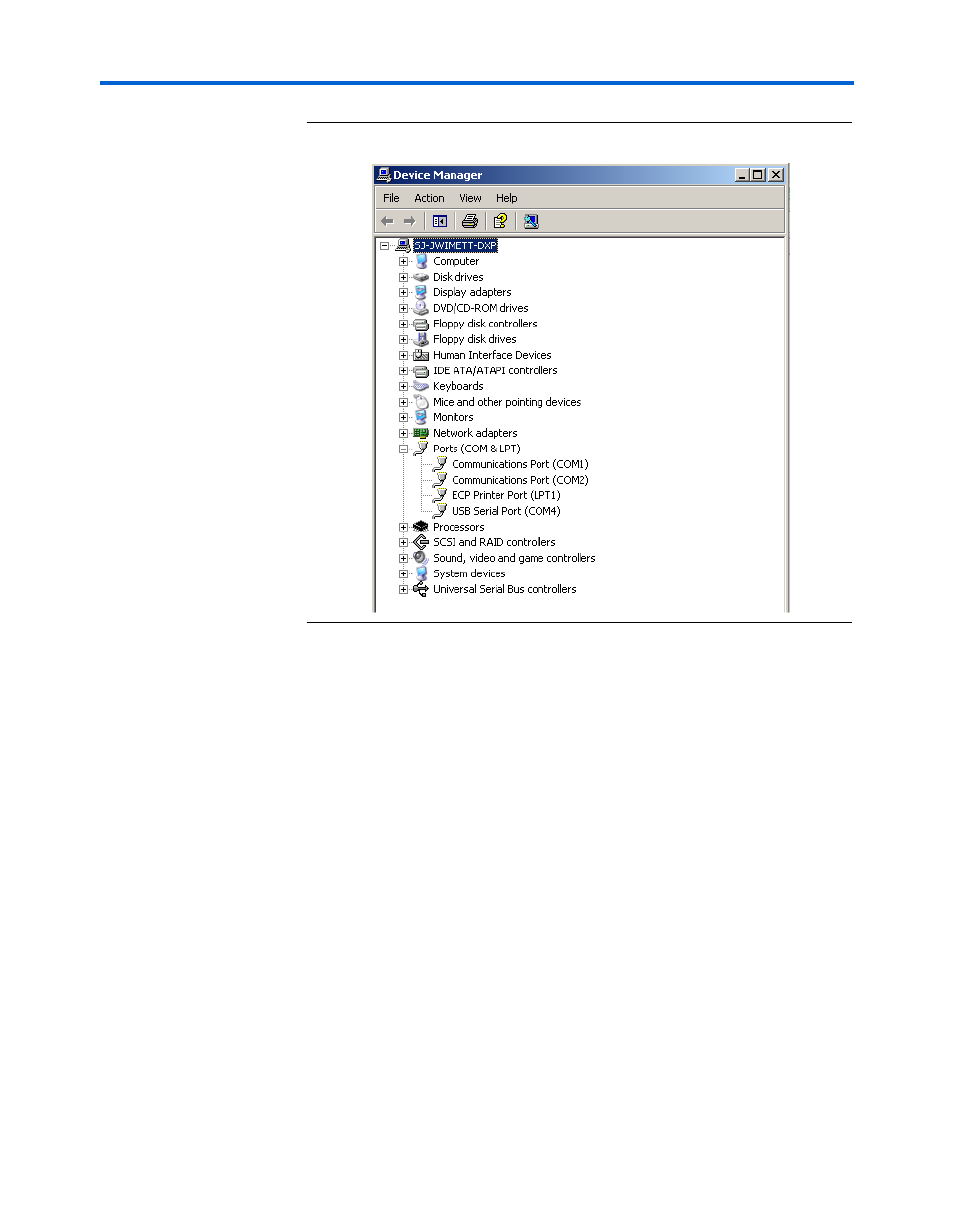

Figure 2–7. Device Manager Window

5.

If successful communication is established, the LCD displays

Connected to PC!

.

6.

The PC Application allows you to read from and write to most of

the components on the MAX II board. Note the Default Encoding

drop down box in the Control Options section of the user interface.

This controls how the MAX II device interprets the data sent to and

received from the MAX II board. If you select Hexadecimal, the PC

will treat all data as hexadecimal characters. If you select ASCII,

then the PC will interpret all data as ASCII.

1

This demo relies on the appropriate transmission of data

from the PC to the board. If corrupt data is transmitted,

errors will occur. The application on the PC may be

unaware of hardware errors. The board will show hardware

errors by flashing the LEDs. If you see that the LEDs are

flashing, click the Close Port button on the PC application

and press S1 on the development board. You can then

re-open the port and use the demo as normal.