Random test, Increment test, The power monitor – Altera Cyclone V GX FPGA User Manual

Page 26: Random test –10 increment test –10, The power monitor –10

6–10

Chapter 6: Board Test System

The Power Monitor

Cyclone V GX FPGA Development Kit

October 2012

Altera Corporation

User Guide

Random Test

Starts a random data pattern test to SSRAM memory

.

Increment Test

Starts an incrementing data pattern test to SSRAM memory

.

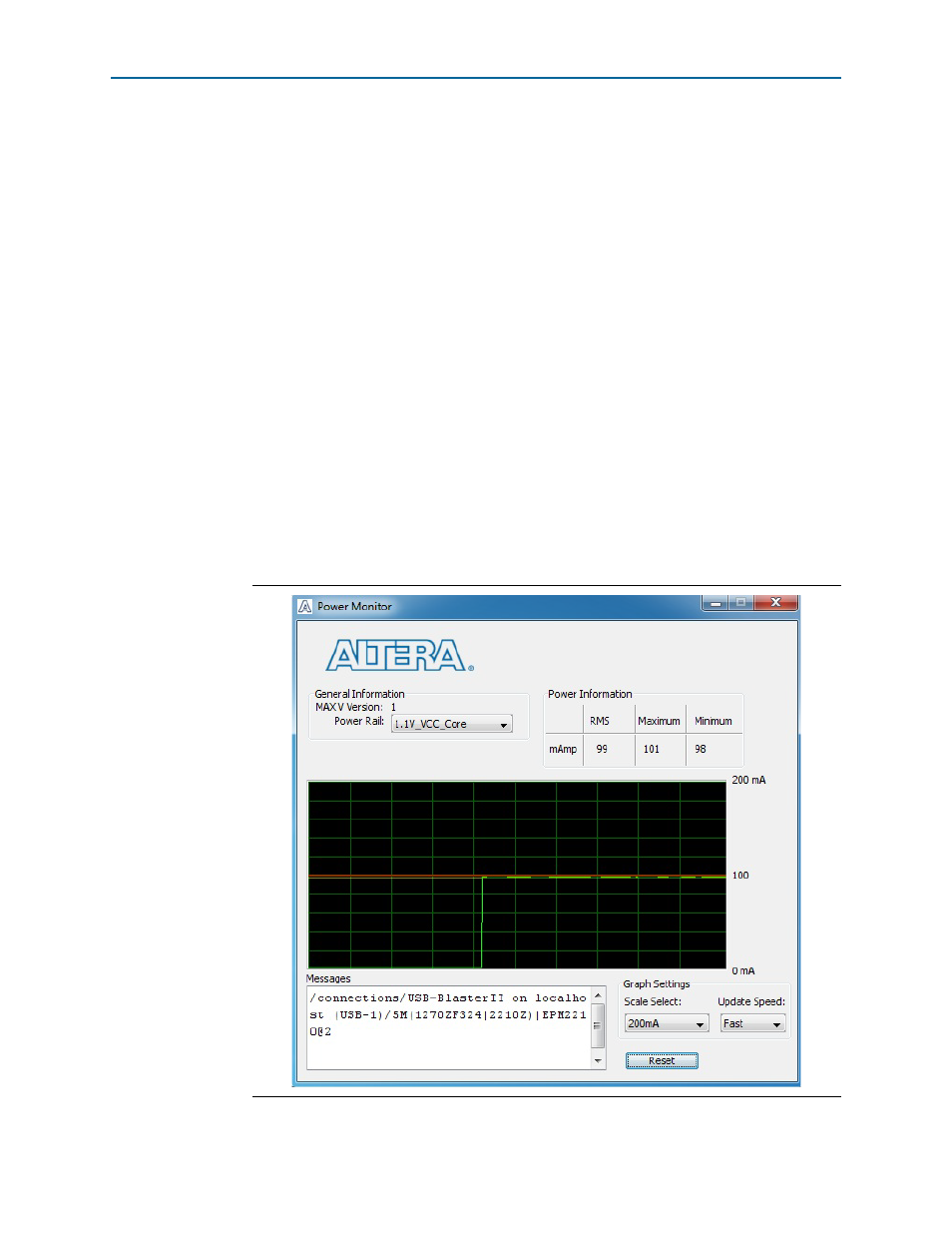

The Power Monitor

The Power Monitor measures and reports current power

information. To start the

application, click Power Monitor in the Board Test System application.

1

You can also run the Power Monitor as a stand-alone application. PowerMonitor.exe

resides in the

On Windows, click Start > All Programs > Altera > Cyclone V GX FPGA

Development Kit

<version> > Power Monitor to start the application.

The Power Monitor communicates with the MAX V device on the board through the

JTAG bus. A power monitor circuit attached to the MAX V device allows you to

measure the power that the Cyclone V GX FPGA is consuming.

shows the

Power Monitor.

Figure 6–5. The Power Monitor