Crc checker, Crc checker –3 – Altera CRC Compiler User Manual

Page 19

Chapter 3: Functional Description

3–3

CRC Checker

© November 2009

Altera Corporation

Preliminary

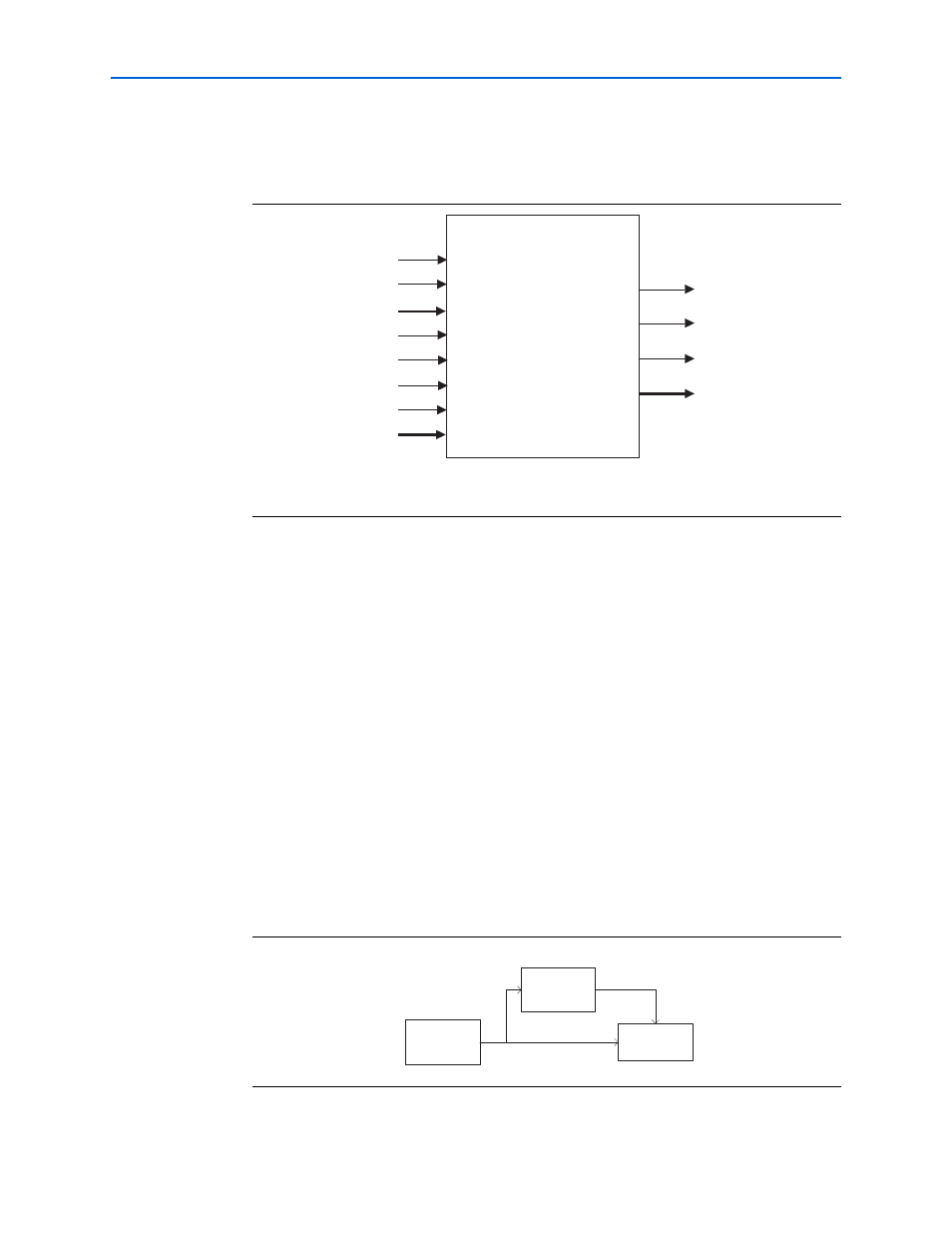

CRC Checker

shows the block diagram for the CRC Checker.

The CRC Compiler MegaCore function receives message and

checksum

(codeword)

bits from the data input interface on each clock cycle during which

datavalid

is

asserted. The

datavalid

signal can be asserted or deasserted arbitrarily during or

between packets as shown in

When

datavalid

is asserted, all

data

pins must contain valid data and the

empty

signal must be zero, with the exception of the final word of a packet. The

empty

signal, if used, must be set to 0 during all cycles except the last word of a packet, that

is when

endofpacket

is asserted. If

datavalid

is deasserted,

data

,

startofpacket

,

endofpacket

, and

empty

are ignored. Following a fixed number

of clock cycles after the final word, indicated by assertion of

endofpacket

,

crcvalid

is asserted and the

crcbad

output is set to 1 if the calculated syndrome is

incorrect. The value of

crcbad

is undefined at other times. For the delay between

assertion of

endofpacket

and

crcvalid

, refer to the Latency panel of the

MegaWizard interface.

The CRC checker can start computing the checksum of a new packet while it is

completing the calculation for the previous packet, that is before it asserts

crcvalid

.

The data source may assert

startofpacket

on the clock cycle immediately

following

endofpacket

, regardless of the checker's latency.

Figure 3–4. CRC Checker Block Diagram

Note to

:

(1) These signals are present only in a multi-channel checker.

Figure 3–5. Typical CRC Checker Application

clk

reset_n

data

crcchannel

(1)

datavalid

startofpacket

endofpacket

crcbad

datachannel

(1)

chaninitdone

(1)

CRC CHECKER

empty

crcvalid

Receiver

CRC

Checker

Codeword bits

Data sink

crcbad