Functional description, Functional overview, Crc generator – Altera CRC Compiler User Manual

Page 17: Chapter 3. functional description, Functional overview –1 crc generator –1

© November 2009

Altera Corporation

Preliminary

3. Functional Description

Functional Overview

The CRC Compiler MegaCore function generates high-performance circuits to

generate or check Cyclic Redundancy Check checksums for packet-based

communication. The CRC Compiler dynamically generates RTL based on

requirements you supply, rather than parameterizing static RTL.

The generated CRC MegaCore function uses an Avalon-ST interface to receive data.

Generated checksums for transmission or the status of received checksums are

emitted on dedicated ports. The CRC MegaCore function does not provide an

Avalon

®

Memory-Mapped (Avalon-MM) interface or any other software access

interface. The generated CRC MegaCore function also does not store any data,

checksums, or status.

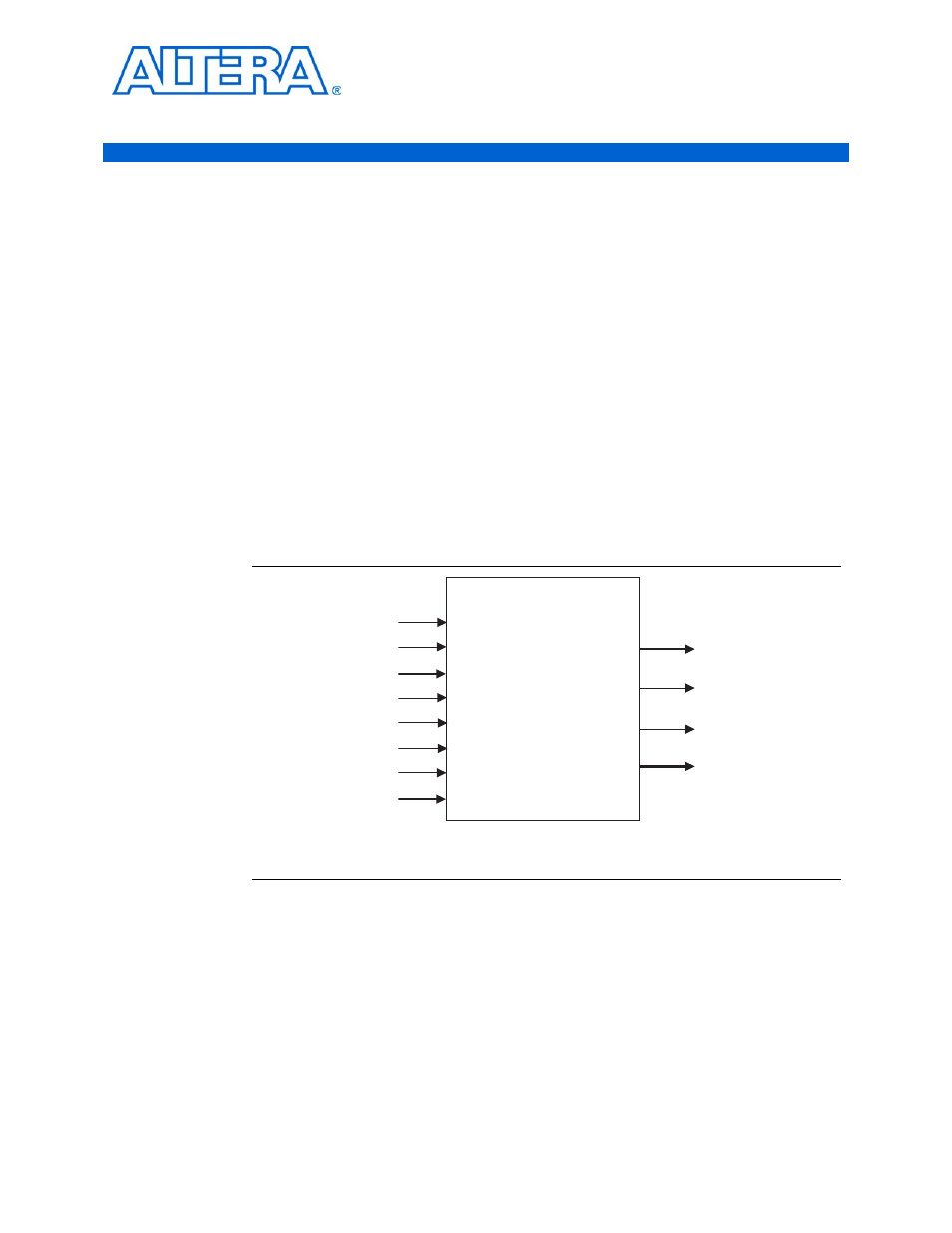

CRC Generator

shows the block diagram of the CRC generator.

The CRC Generator receives message bits from the data input interface on each clock

cycle during which

datavalid

is asserted. The

datavalid

signal may be asserted

or deasserted arbitrarily during or between packets. When

datavalid

is asserted,

all data pins must contain valid data and the empty signal must be zero, with the

exception of the final word of a packet. The

empty

signal, if used, must be set to zero

during all cycles except the last word of a packet, that is when

endofpacket

is

asserted. If

datavalid

is deasserted,

data

,

startofpacket

,

endofpacke

t, and

Figure 3–1. CRC Generator Block Diagram

Note to

:

(1) These signals are present only in a multi-channel generator.

clk

reset_n

data

crcchannel

(1)

datavalid

startofpacket

endofpacket

checksum

datachannel

(1)

chaninitdone

(1)

CRC GENERATOR

empty

crcvalid