Avalon-st interfaces in dsp ip cores, Avalon-st interfaces in dsp ip cores -10 – Altera CIC MegaCore Function User Manual

Page 26

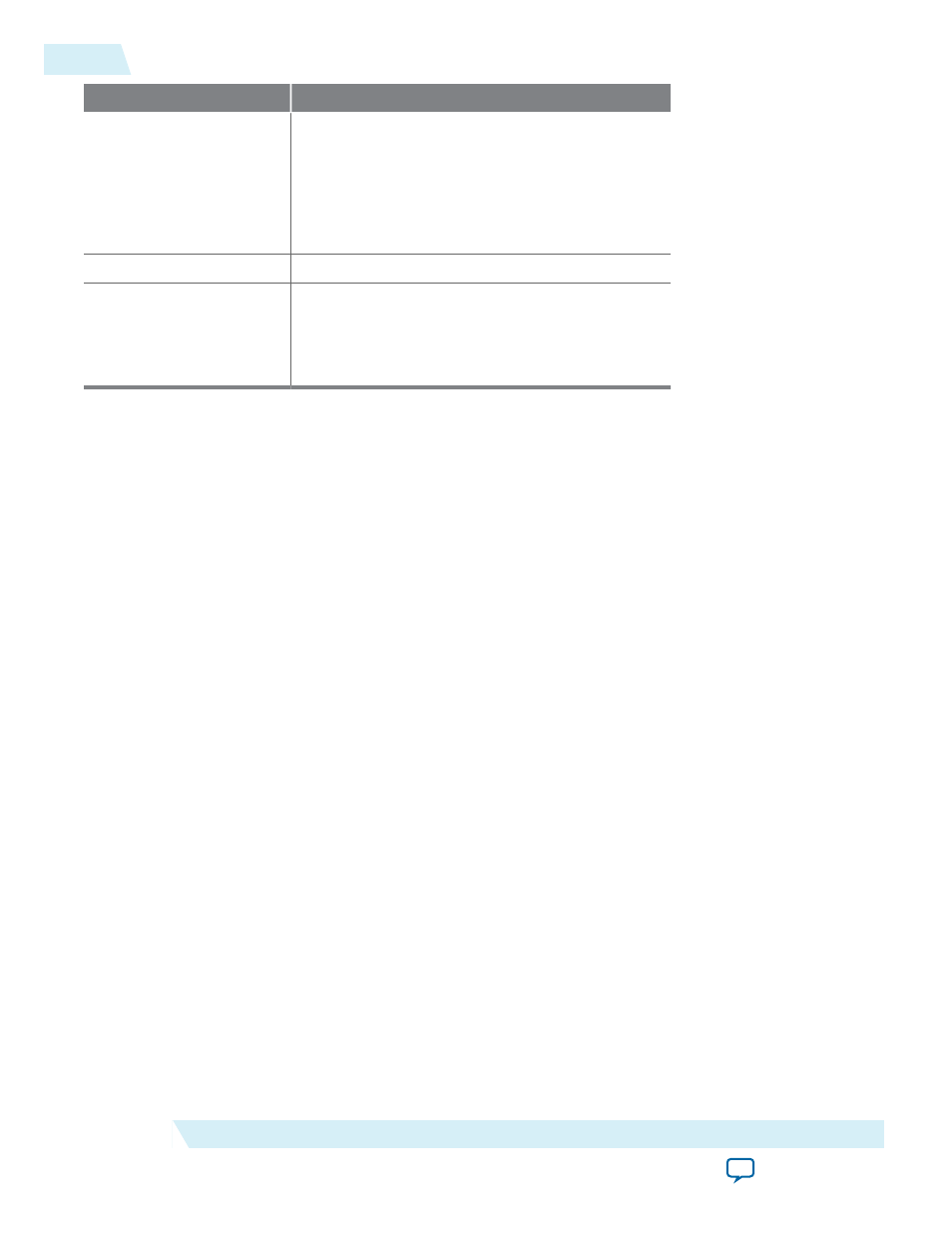

Parameter Name

Value

SYMBOLS_PER_BEAT

Single input, single output architectures, have one

symbol per beat at the source and the sink. MISO

architectures have

per beat at the sink, and a single symbol per beat

at the source. SIMO architectures have

of interfaces> symbols per beat at the source, and a

single symbol per beat at the sink.

SYMBOL_TYPE

Signed

ERROR_DESCRIPTION

• 00: No error

• 01: Missing

startofpacket

(SOP)

• 10: Missing

endofpacket

(EOP)

• 11: Unexpected EOP or any other error

Related Information

For more information about the Avalon-ST interface

Avalon-ST Interfaces in DSP IP Cores

Avalon-ST interfaces define a standard, flexible, and modular protocol for data transfers from a source

interface to a sink interface.

The input interface is an Avalon-ST sink and the output interface is an Avalon-ST source. The Avalon-ST

interface supports packet transfers with packets interleaved across multiple channels.

Avalon-ST interface signals can describe traditional streaming interfaces supporting a single stream of

data without knowledge of channels or packet boundaries. Such interfaces typically contain data, ready,

and valid signals. Avalon-ST interfaces can also support more complex protocols for burst and packet

transfers with packets interleaved across multiple channels. The Avalon-ST interface inherently synchro‐

nizes multichannel designs, which allows you to achieve efficient, time-multiplexed implementations

without having to implement complex control logic.

Avalon-ST interfaces support backpressure, which is a flow control mechanism where a sink can signal to

a source to stop sending data. The sink typically uses backpressure to stop the flow of data when its FIFO

buffers are full or when it has congestion on its output.

Related Information

•

3-10

Avalon-ST Interfaces in DSP IP Cores

UG-CIC

2014.12.15

Altera Corporation

CIC IP Core Functional Description