Watchdog fault, Status + hart instances (101) – Spectrum Controls 1734sc-OE2CIH User Manual

Page 49

Chapter 4: OE2CIH and HART

4-13

User’s Manual Pub. 0300272-01 Rev. A.0

Watchdog Fault

In the case where the main CPU experiences a watchdog failure, the following will take

place:

1. The module resets.

2. Once the watchdog reset is detected at startup, both channels are held in reset.

3. The Module Status is set to 1.

4. Both Channel Statuses are set to the HF bit.

5. The Module Status LED blinks Red, and Channel Status LEDs are solid Red.

6. Any configuration sent to the module is ignored.

7. Firmware updates are allowed when in this state.

Status + HART Instances (101)

If HART or the channel is disabled, the HART data will be all zeros.

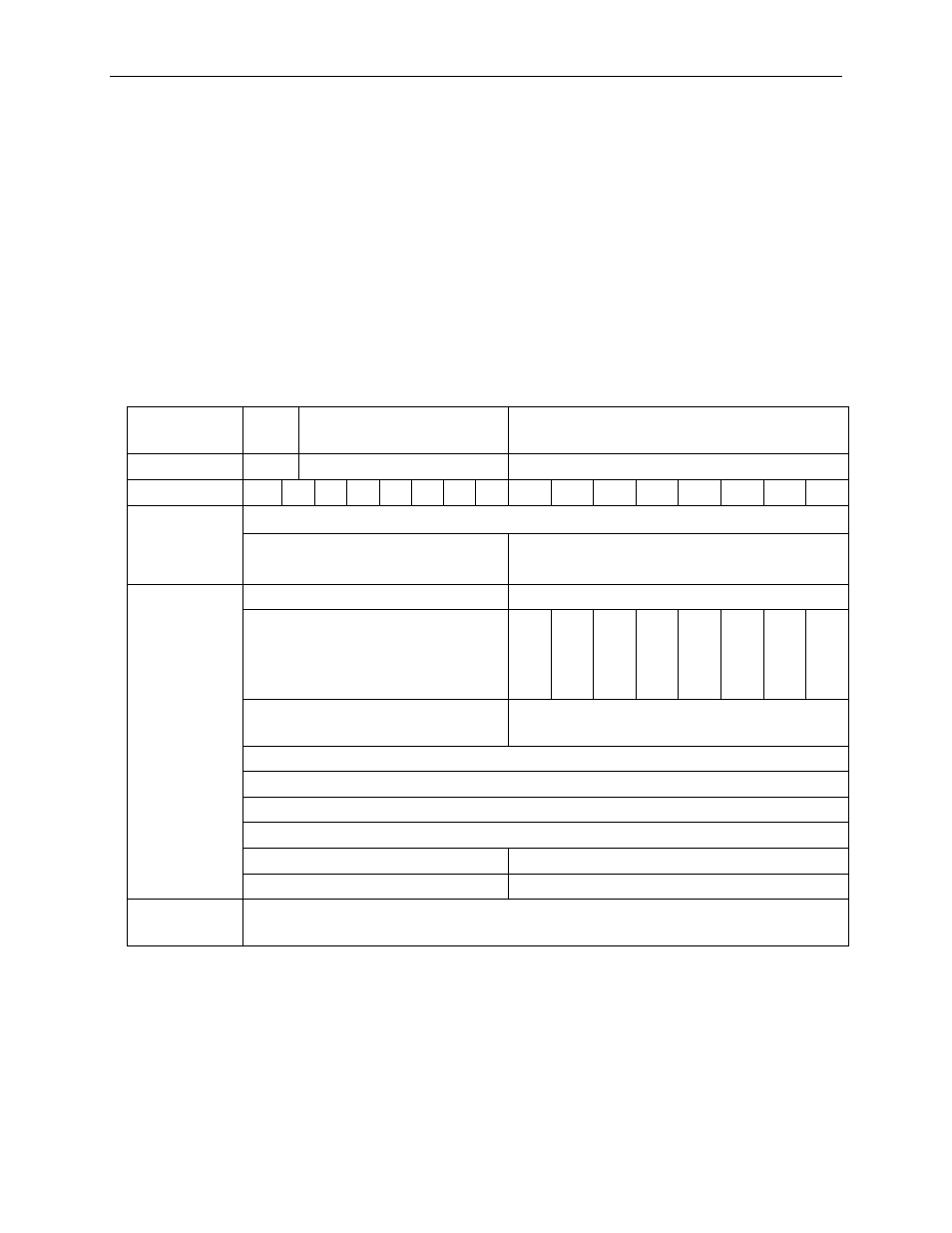

Table 4-9 Channel Input + HART Assembly

Instance:

101

ID:

3

Description:

Status + Hart 0,1

Total Size:

56 Bytes RSL 5 K (DeviceNet 52 bytes)

Bit

15 14 13 12 11 10 09 08

07

06

05

04

03

02

01

00

Analog data

4 bytes

0×00 to 0×03

Module Status

High Byte–Channel 1 Status

Low Byte–Channel 0 Status

Ch. 0 Hart Data

24 bytes

0×04 to 0×1C

Channel 0 Hart Device Status Byte 1

Channel 0 Hart Device Status Byte 0

Communication Status /

Response Code

FAUL

T

SUA

DDL

GX

DDL

DR

MSGRD

Y

MA

FL

T

FAI

L

INI

T

Channel 0 Hart Device Status Byte 3

Extended Device Status Byte

Channel 0 Hart Device Status Byte 2

Field Device Status Byte

Channel 0 Hart PV–REAL (float) 4 bytes

Channel 0 Hart SV–REAL (float) 4 bytes

Channel 0 Hart TV–REAL (float) 4 bytes

Channel 0 Hart FV–REAL (float) 4 bytes

Channel 0 Hart SV Status byte

Channel 0 Hart PV Status byte

Channel 0 Hart FV Status byte

Channel 0 Hart TV Status byte

Ch. 1 Hart Data

0×1D to 0×39

(Data structure same as Channel 0 above 24 bytes)