Row a, Signal descriptions (cont’d) – ADLINK nanoX-TC User Manual

Page 17

Page 17

Express-IA533 User’s Manual

Page 17

Express-IA533 User’s Manual

nanoX-TC User’s Manual

Page 17

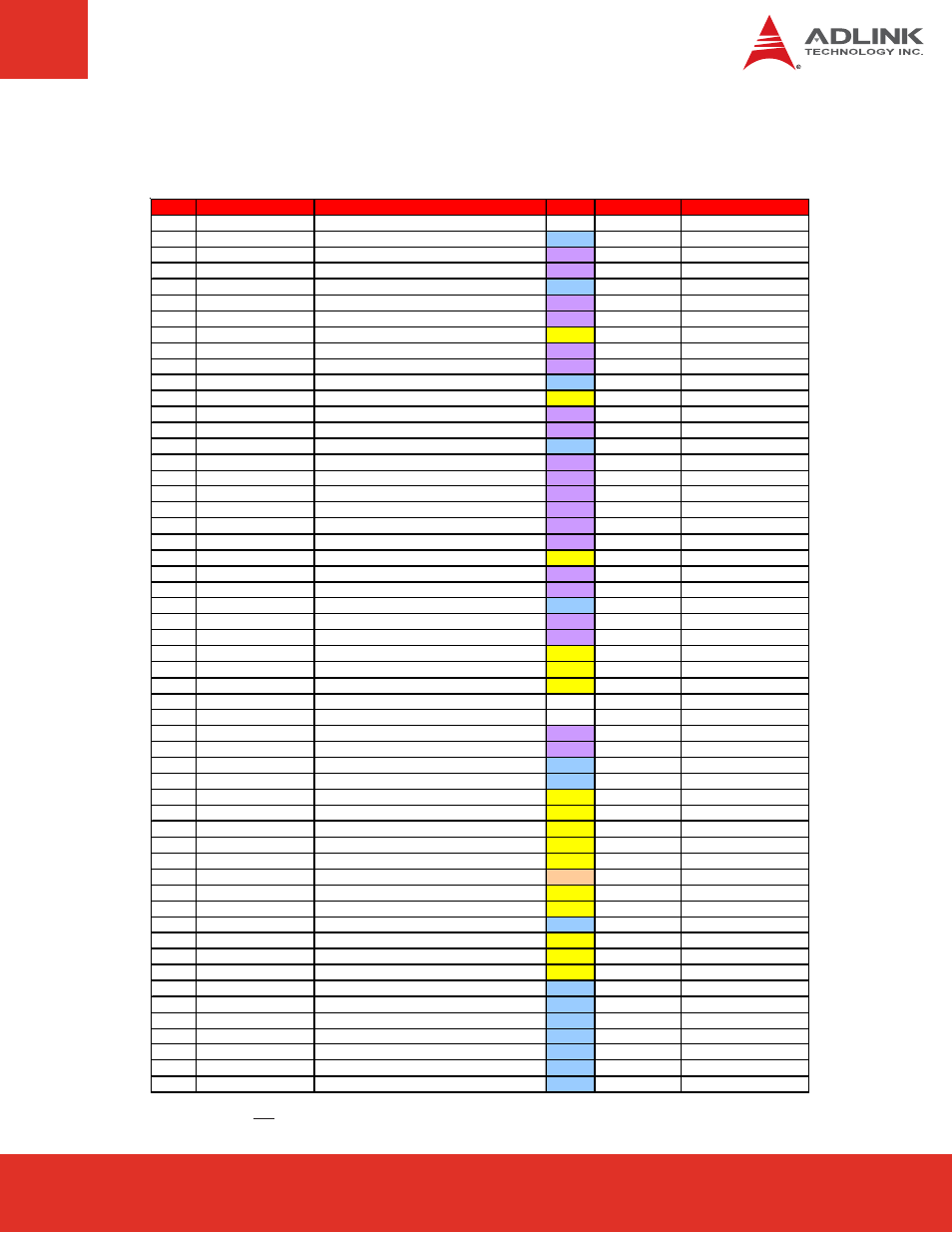

Row A

Signal Descriptions (cont’d)

Pin

Signal

Description

Type

PU/PD

Comment

A56

RSVD

NC

-

-

A57

G ND

Ground

P WR

-

-

A58

P CIE _TX3+

P CIe 3 TX+ (port 0 of CP U, occupied)

O - DP

-

used for PC H E G20T

A59

P CIE _TX3-

P CIe 3 TX- (port 0 of CPU, occupied)

O - DP

-

used for PC H E G20T

A60

GND(FIXE D)

Ground

P WR

-

-

A61

P CIE _TX2+

P CIe 2 TX+ (port 3 of CP U)

O - DP

-

-

A62

P CIE _TX2-

P CIe 2 TX- (port 3 of CPU)

O - DP

-

-

A63

GPI1

GP I1 or SDIO controller 0 data 1

IO-3.3

P U 10k 3.3V

BIOS select

A64

P CIE _TX1+

P CIe 1 TX+ (port 2 of CP U)

O - DP

-

-

A65

P CIE _TX1-

P CIe 1 TX- (port 2 of CPU)

O - DP

-

-

A66

G ND

Ground

P WR

-

-

A67

GPI2

GP I2 or SDIO controller 0 data 2

IO-3.3

P U 10k 3.3V

BIOS select

A68

P CIE _TX0+

P CIe 0 TX+ (port 1 of CP U)

O - DP

-

-

A69

P CIE _TX0-

P CIe 0 TX- (port 1 of CPU)

O - DP

-

-

A70

GND(FIXE D)

Ground

P WR

-

-

A71

LVDS_ A0+

LVDS Channel A

O - DP

-

-

A72

LVDS_ A0-

LVDS Channel A

O - DP

-

-

A73

LVDS_ A1+

LVDS Channel A

O - DP

-

-

A74

LVDS_ A1-

LVDS Channel A

O - DP

-

-

A75

LVDS_ A2+

LVDS Channel A

O - DP

-

-

A76

LVDS_ A2-

LVDS Channel A

O - DP

-

-

A77

LVDS_ VDD_ EN

LVDS VDD Panel Power

O-2,5

PD 10k

-

A78

LVDS_ A3+

LVDS Channel A

O - DP

-

-

A79

LVDS_ A3-

LVDS Channel A

O - DP

-

-

A80

GND(FIXE D)

Ground

P WR

-

-

A81

LVDS _A_ CK+

LVDS Channel A Clock

O - DP

-

-

A82

LVDS _A_ CK-

LVDS Channel A Clock

O - DP

-

-

A83

LVDS_I2C _CK

LVDS I2C Clock

IO-3.3

PU 2.2k 3.3V

-

A84

LVDS_I2C _DAT

LVDS I2C Data

IO-3.3

PU 2.2k 3.3V

-

A85

GPI3

GP I3 or SDIO controller 0 data 3

IO-3.3

P U 10k 3.3V

BIOS select

A86

RSVD

NC

-

-

A87

RSVD

NC

-

-

A88

PCIE_ CLK_REF +

P CI E xpress Clock Reference

O - DP

-

-

A89

PCIE _ CLK _RE F-

P CI E xpress Clock Reference

O - DP

-

-

A90

GND(FIXE D)

Ground

P WR

-

-

A91

SPI_ POWE R

P ower source for SPI devices on carrier

P WR

-

-

A92

S PI_MISO

Data in to Module from Carrier S PI

I-3.3

-

A93

GPO0

GP O0 or S DIO controller 0 clock

O-3.3

P U 10k 3.3V

BIOS select

A94

S PI_CLK

Clock from Module to Carrier SP I

O-3.3

-

A95

S PI_MOSI

Data out from Module to C arrier SPI

O-3.3

-

A96

TPM_P P

(TPM) Physical Presence pin

I-3.3

-

A97

TYP E 10#

Rev 2.0 / Type 10 indicator to carrier

STO

PD 4.7k

-

A98

SE R0_TX

S erial 0 port transmitter

O-5

-

A99

SER0_RX

S erial 0 port receiver

I-5

-

A100

GND(FIXE D)

Ground

P WR

-

-

A101

SE R1_TX

S erial 1 port transmitter / or CAN CAN_AX

O-5

-

A102

SER1_RX

S erial 1 port receiver / or CAN CAN_ RX

I-5

-

A103

LID#

ACPI type LID switch

I-3.3

PU 4.7k 3.3V

A104

VCC_ 12V

P ower 12V

P WR

-

-

A105

VCC_ 12V

P ower 12V

P WR

-

-

A106

VCC_ 12V

P ower 12V

P WR

-

-

A107

VCC_ 12V

P ower 12V

P WR

-

-

A108

VCC_ 12V

P ower 12V

P WR

-

-

A109

VCC_ 12V

P ower 12V

P WR

-

-

A110

GND(FIXE D)

Ground

P WR

-

-

XXX Strikethrough pin names indicates that the signal is not supported on this module.