Cypress CY7C1332AV25 User Manual

Preliminary

PRELIMINARY

18-Mbit (512K x 36/1Mbit x 18)

Pipelined Register-Register Late Write

CY7C1330AV25

CY7C1332AV25

Cypress Semiconductor Corporation

•

198 Champion Court

•

San Jose

,

CA 95134-1709

•

408-943-2600

Document No: 001-07844 Rev. *A

Revised September 20, 2006

Features

• Fast clock speed: 250, 200 MHz

• Fast access time: 2.0, 2.25 ns

• Synchronous Pipelined Operation with Self-timed Late

Write

• Internally synchronized registered outputs eliminate

the need to control OE

• 2.5V core supply voltage

• 1.4–1.9V V

DDQ

supply with V

REF

of 0.68–0.95V

— Wide range HSTL I/O Levels

• Single Differential HSTL clock Input K and K

• Single WE (READ/WRITE) control pin

• Individual byte write (BWS

[a:d]

) control (may be tied

LOW)

• Common I/O

• Asynchronous Output Enable Input

• Programmable Impedance Output Drivers

• JTAG boundary scan for BGA packaging version

• Available in a 119-ball BGA package (CY7C1330AV25

and CY7C1332AV25)

Configuration

CY7C1330AV25 – 512K x 36

CY7C1332AV25 – 1M x 18

Functional Description

The CY7C1330AV25 and CY7C1332AV25 are high perfor-

mance, Synchronous Pipelined SRAMs designed with late

write operation. These SRAMs can achieve speeds up to 250

MHz. Each memory cell consists of six transistors.

Late write feature avoids an idle cycle required during the

turnaround of the bus from a read to a write.

All synchronous inputs are gated by registers controlled by a

positive-edge-triggered Clock Input (K). The synchronous

inputs include all addresses (A), all data inputs (DQ

[a:d]

), Chip

Enable (CE), Byte Write Selects (BWS

[a:d]

), and read-write

control (WE). Read or Write Operations can be initiated with

the chip enable pin (CE). This signal allows the user to

select/deselect the device when desired.

Power down feature is accomplished by pulling the

Synchronous signal ZZ HIGH.

Output Enable (OE) is an asynchronous input signal. OE can

be used to disable the outputs at any given time.

Four pins are used to implement JTAG test capabilities. The

JTAG circuitry is used to serially shift data to and from the

device. JTAG inputs use LVTTL/LVCMOS levels to shift data

during this testing mode of operation.

K,K

A

x

WE

BWS

x

CE

OE

512Kx36

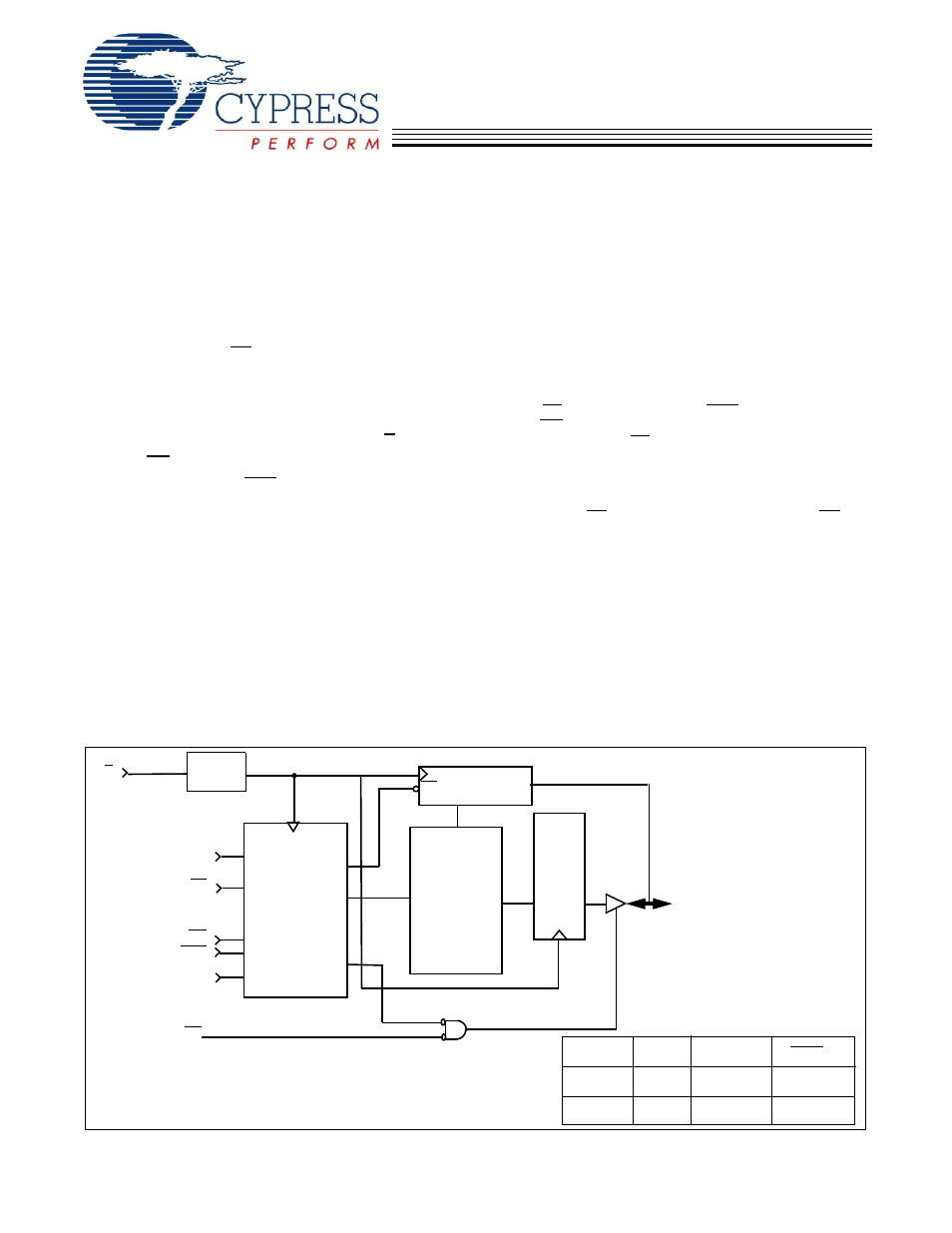

Logic Block Diagram

DQ

x

Data-In REG.

Q

D

CE

CONTROL

and WRITE

LOGIC

ZZ

1Mx18

OUT

O

UT

REGISTERS

a

nd L

OGIC

512Kx36

1Mx18

A

X

DQ

X

BWS

X

X = 18:0

X = 19:0

X = a, b

X = a, b, c, d

X = a, b

X = a, b, c, d

Clock

Buffer

MEMORY

ARRAY

(2stage)