Figure a-1 front panel, A.1.2 cpu module, A.1.2 – Cabletron Systems SmartCell 6A000 User Manual

Page 66

Appendix A-2 SmartCell 6A000 User Guide

Hardware Components

Features and Specifications

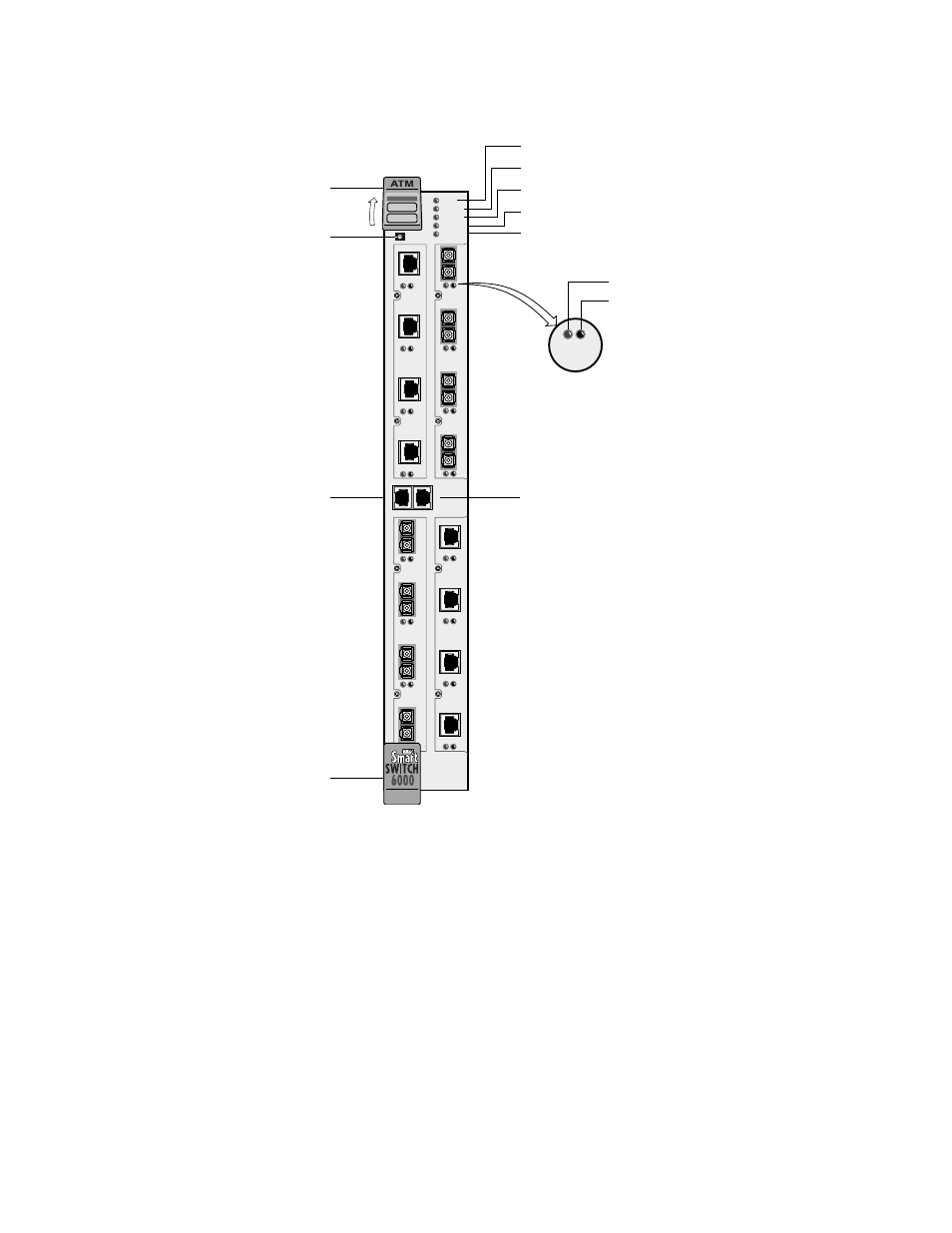

Figure A-1 Front panel

A.1.2

CPU Module

The CPU module provides control, signaling, and LAN server functions for the switch. A 32-bit RISC processor

(i960CF, 33 MHz) operates all switch software options.

An on-board Segmentation and Reassembly (SAR) ASIC provides rapid packet processing. A common DRAM bank

stores both CPU data structures and SAR processing buffers. Sixteen megabytes of DRAM is standard; 64 MB is

optional.

512 KB SRAM supports up to 4096 VCs routed through the CPU module.

NO SYNC

D

ATA

NO SYNC

D

ATA

1

2

3

4

1234

6A-IOM-21-4

6A-IOM-22-4

FAIL

STATUS

POWER

RX ENET

TX ENET

S

Y

S

T

E

M

C

O

M

A

C

NO SYNC

D

ATA

NO SYNC

D

ATA

1234

6A-IOM-22-4

123

4

6A-IOM-21-4

B

D

E

T

H

E

R

N

E

T

Console Terminal

(RJ-45)

Ethernet Port

(10Base-T)

FAIL

STATUS

POWER

RX DATA

TX DATA

NO SYNC

DATA

Ejector

Reset Button

Ejector

NO SYNC

D

ATA

- 2E42-27R (164 pages)

- 6H122-16 (158 pages)

- 24 (35 pages)

- 9T427-16 (16 pages)

- bridges (132 pages)

- CSX200 (88 pages)

- 2208 (158 pages)

- SM-CSI1076 (69 pages)

- SEHI-22 (93 pages)

- 9T425-16 (40 pages)

- 6000 (180 pages)

- 1800 (448 pages)

- ESX-1380 (86 pages)

- DLE23-MA (202 pages)

- 2E43-51 (168 pages)

- 5000 (83 pages)

- 6H253-13 (62 pages)

- Lancast Media Converter 7000 (108 pages)

- 9G421-02 (12 pages)

- SEH-22 (56 pages)

- 9A000 (180 pages)

- SEH-24 (64 pages)

- 6E123-26 (184 pages)

- STS16-20R (258 pages)

- 2E43-27 (164 pages)

- Cabletron MicroLAN 9E132-15 (36 pages)

- 9F120-08 (28 pages)

- 9E428-36 (18 pages)

- Device Management Module Dec GigaSwitch (65 pages)

- ELS10-26TX (18 pages)

- MICROMMAC-22T (105 pages)

- CSX1200 (644 pages)

- 7H02-06 (36 pages)

- 150 (106 pages)

- 9F206-02 (10 pages)

- MMAC-Plus 9T122-24 (27 pages)

- SEH100TX-22 (52 pages)

- 7C03 MMAC (16 pages)

- 2H253-25R (64 pages)

- TRXI-42 (92 pages)

- 7C04 (150 pages)

- 2H22 (120 pages)

- 2000 (196 pages)

- 7C04 Workgroup (25 pages)