61 s60 – bit mapped test control register, 62 s61 – signal detect register 1, S60 – bit mapped test control register – Maxim Integrated 73M2901CE AT Command User Manual

Page 36: S61 – signal detect register 1

73M2901CE AT Command User Guide

UG_2901CE_027

36

Rev.

2.0

4.4.61

S60 – Bit Mapped Test Control Register

(Default = 0)

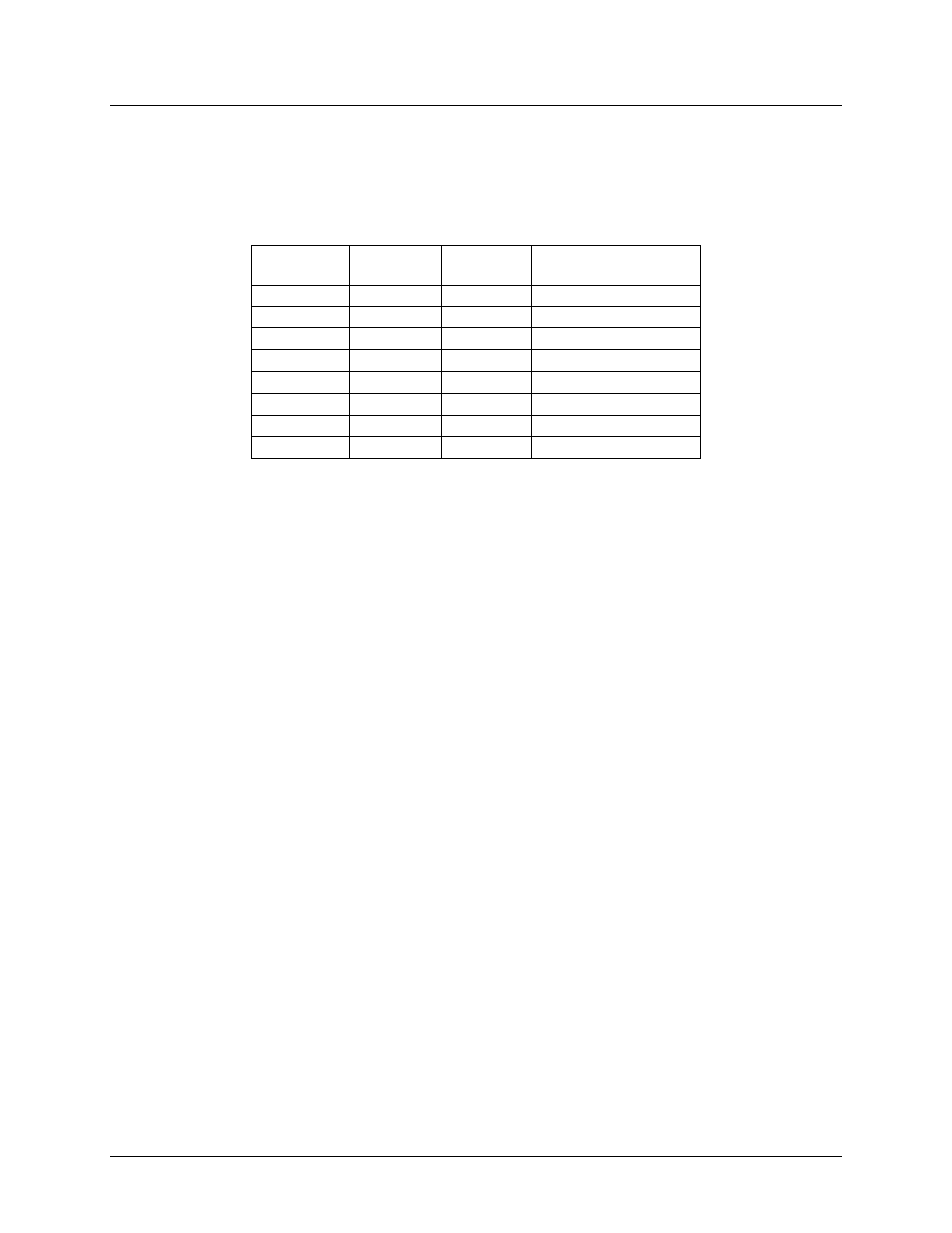

Register S60 reflects the status of test control options and the generation of data patterns. Register S60

is a bit mapped register whose bits are defined as follows:

Bit 4

Bit 1

SDP1

Bit 0

SDP0

Function

0

0

0

Data Mode (default)

0

0

1

Send Marks

0

1

0

Send Spaces

0

1

1

Send Dotting ‘5’

1

0

0

Send S1

1

0

1

Send S0

1

1

0

Send Dotting ‘A’

1

1

1

Send Flags

Bit 3 Enable detection of dial tone.

Bit 4 0 = Disables the scrambler (default).

1 = Enables the scrambler.

Bit 5 0 = Disables the de-scrambler (default).

1 = Enables the de-scrambler.

Bit 6 In RDLB mode.

Bit 7 In ALB mode.

Note: In V.22 and V.22bis modes, the first pattern out of reset should not be spaces, the scrambler needs to

be primed with another pattern.

4.4.62

S61 – Signal Detect Register 1

(Default = 0)

Register S61 reflects the status of various options. It is only valid in Data mode. Register S61 is a bit

mapped register that behaves in the following manner when its bits are set:

Bit 0 Causes S62 or S65 (J6) to be sent out USER PORT 2 (available in a special test package only).

Bit 1 Remote digital loopback enabled (equivalent to @T4).

Bit 2 Carrier detect bit. This bit will be set when conditions for V.24 circuit 104 have been met by the

modulation mode being connected.

Bit 3

Wait for Calling Tone before sending Answer Tone.

Bit 4 In Call Progress: Energy detect bit. This bit will be set if the receive level is above a certain

threshold.

In Data Mode: Raw Carrier Detect bit.

Bit 5 S1 Detect bit. This will be set if S1 (unscrambled 1100Hz) is detected. This bit is also used to

detect a retrain request if connected in V.22 bis or V.22