2 visa-2 loopback test, Visa-2 loopback test, Figure 15: visa-2 loopback test flow chart – Maxim Integrated 73S12xxF Software User Manual

Page 91

UG_12xxF_016

73S12xxF Software User Guide

Rev. 1.50

91

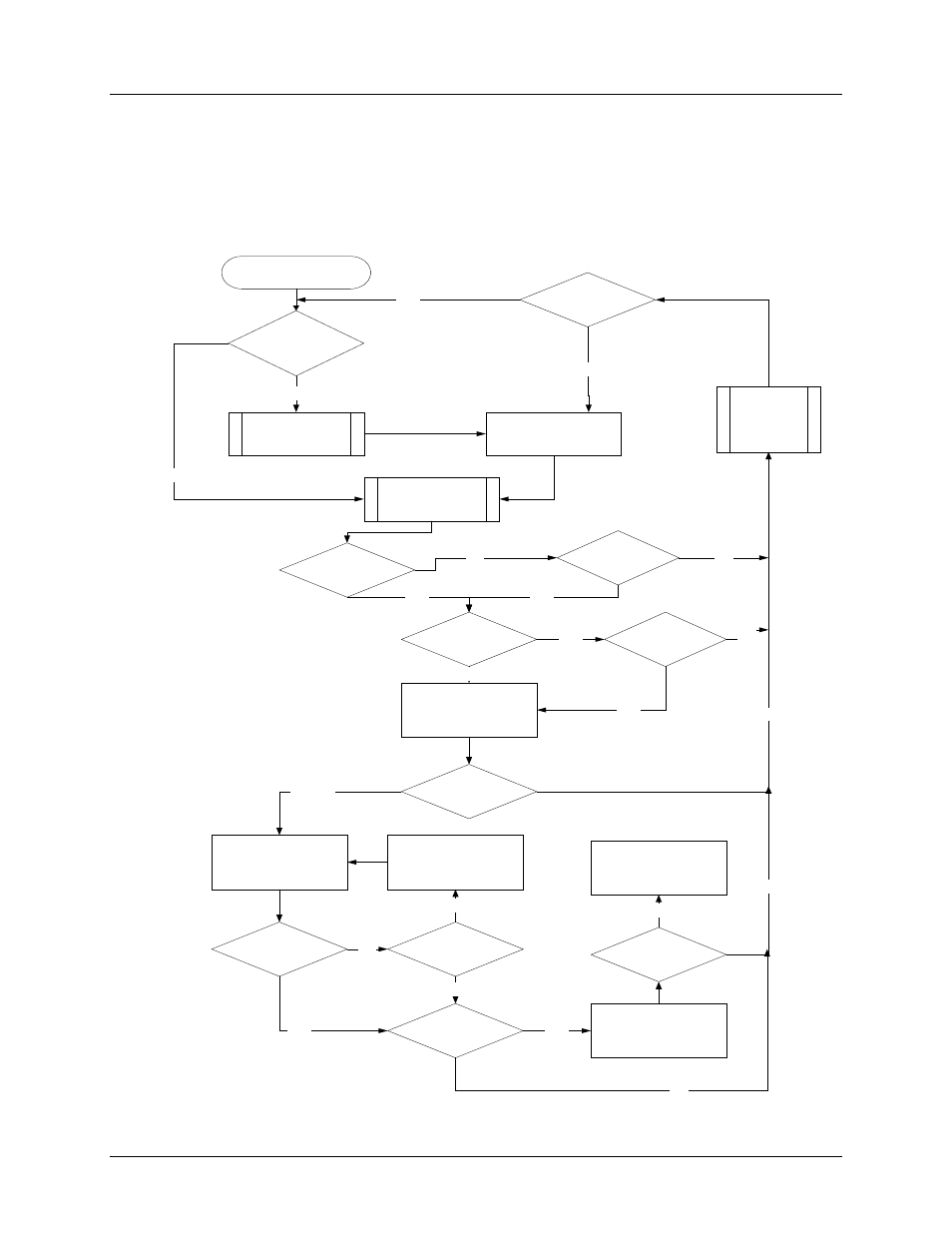

4.5.2 VISA-2 Loopback Test

Teridian used the ICT-K test lab in Korea (listed on th

website) for VISA-2 loopback

testing. This lab used the VISA test suite version 4.1 for their EMV Level I qualification test services

(details shown in

). The USB CCID firmware includes the source code that implements this

test.

Initialization

Enter Delay Time

(in Secs)

Power-Up Ok

(Good ATR)?

SELECT FILE

1PAY.SYS.DDF01

EMV Power

Down

M/m

Any other Key

Warm Reset OK?

Yes

No

No

Exchange OK?

End of Record?

or No Record?

Enter (M/m) Multi-

or (anykey) Single

Shot?

Delay Time Wait

EMV Power Up

Negotiable Mode?

No

PPS OK?

Yes

SingleShot?

Yes

No

No

Yes

No

Yes

READ RECORD

(00 B2 'P1' 0C 00)

Yes

P1 = 01

Increment RECORD

Index (P1)

Yes

No

Exchange OK?

No

T-AID Present

T-Select AID Command

Yes

Yes

Exchange OK?

No

Yes

No

T-Book1 - 12.4 Step 1

T - 00A404000CA00000000310100000000001

Figure 15: VISA-2 Loopback Test Flow Chart

- DS80C390 (58 pages)

- DS5001FP (26 pages)

- MAX1416 (14 pages)

- MAX5865 (18 pages)

- DS33Z41 (167 pages)

- MAX1202 (7 pages)

- USBTO232 (31 pages)

- HFAN-09.5.0: Pattern Creator/Converter Software (8 pages)

- MAX-IDE MAXQ Microcontrollers (11 pages)

- MAX6876 Power-Supply Tracker/Sequencer (6 pages)

- MAX6877 Power-Supply Tracker/Sequencer (3 pages)

- 78Q8430 ARM9(920T) Linux Driver Diagnostic Guide (19 pages)

- 78Q8430 Software Driver (54 pages)

- 78Q8430 ST 5100/OS-20 with NexGen TCP/IP Stack (28 pages)

- 6612_OMU_S2_URT_V1_13 (56 pages)

- 6612_OMU_S2+2_URT_V1_14 (58 pages)

- 71M6511 Power Meter IC Family Software (137 pages)

- 71M65xx ADM51 ICE Safety Notice (2 pages)

- 71M6511 2-Layer Demo Board (2 pages)

- 71M6511 4-Layer Demo Board (2 pages)

- 78Q8430 Linux Driver ARM Platform (22 pages)

- 71M6513 Demo Board (2 pages)

- 71M6521DE Energy Meter IC Family Software (138 pages)

- 71M6521 Demo Board (2 pages)

- 71M6531 Demo Board (2 pages)

- 71M6531 Energy Meter IC Family Software (116 pages)

- 71M6533 Demo Board (2 pages)

- 71M6534H Demo Board (2 pages)

- 71M6515H Demo Board (2 pages)

- 73S1209F Evaluation Board (2 pages)

- 73S12xxF (38 pages)

- 73S1210F Evaluation Board Lite (2 pages)

- 73S1210F Evaluation Board (2 pages)

- 73S1210F Multi-SAM Evaluation Board Lite (2 pages)

- 73S12xxF USB-CCID Linux DFU Host Application (8 pages)

- 73S1215F Device Firmware Upgrade Host Driver/Application (10 pages)

- 73S12xxF USB-CCID Host GUI (22 pages)

- 73S1215F Windows XP 32 USB CCID and DFU Drivers (15 pages)

- 73S1215F CCID USB Linux Driver (16 pages)

- 73S1215F Evaluation Board (2 pages)

- 73S1215F Evaluation Board Lite (2 pages)

- 73S1217F Evaluation Board (2 pages)

- 73S1217F Evaluation Board Lite (2 pages)

- MAXQ Family (216 pages)