Switching characteristics – Cypress CY7C1350G User Manual

Page 9

CY7C1350G

Document #: 38-05524 Rev. *F

Page 9 of 15

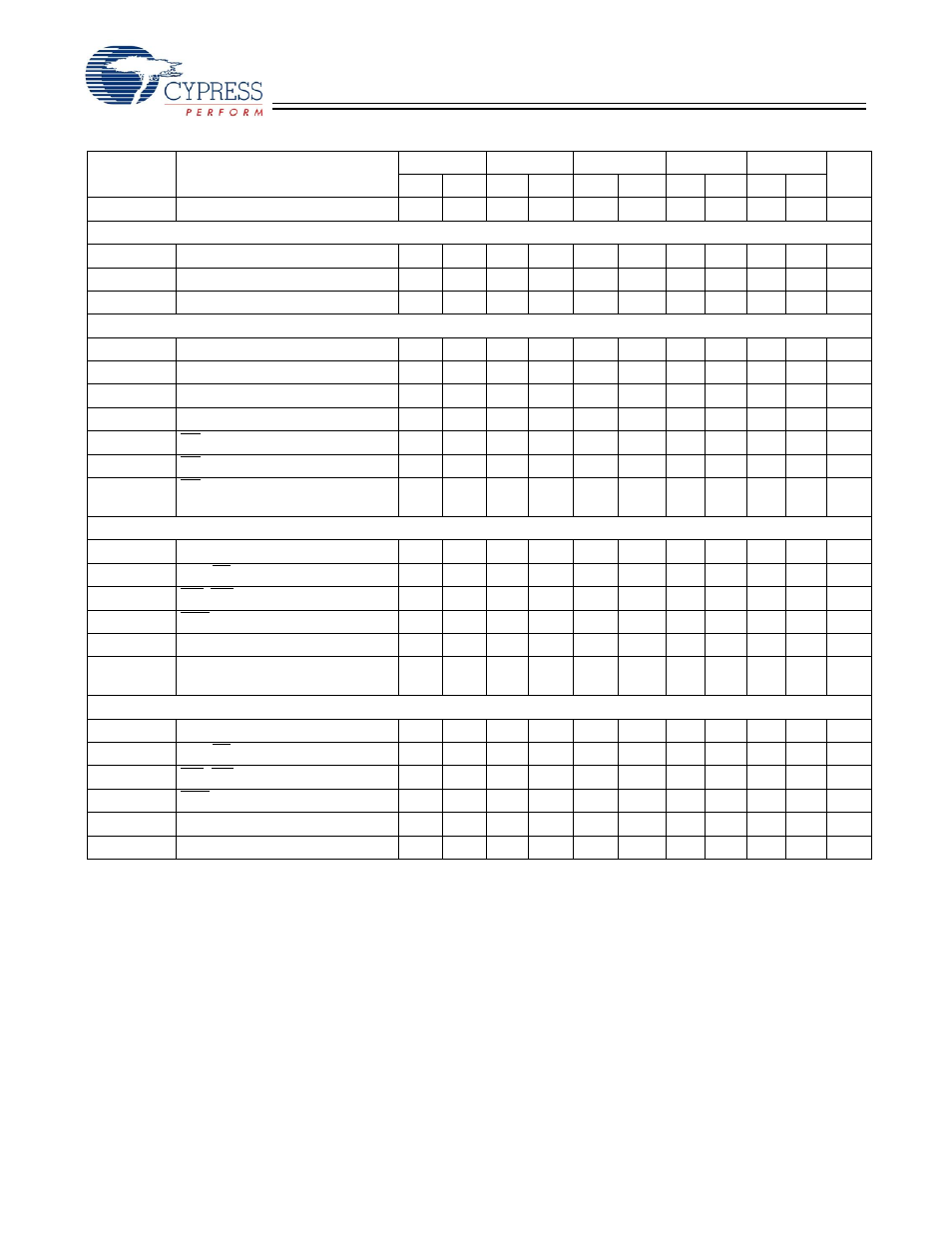

Switching Characteristics

Over the Operating Range

[17, 18]

–250

–200

–166

–133

–100

Parameter

Description

Min.

Max.

Min.

Max.

Min.

Max.

Min. Max. Min. Max.

Unit

t

POWER

V

DD

(typical) to the first Access

[13]

1

1

1

1

1

ms

Clock

t

CYC

Clock Cycle Time

4.0

5.0

6.0

7.5

10

ns

t

CH

Clock HIGH

1.7

2.0

2.5

3.0

3.5

ns

t

CL

Clock LOW

1.7

2.0

2.5

3.0

3.5

ns

Output Times

t

CO

Data Output Valid After CLK Rise

2.6

2.8

3.5

4.0

4.5

ns

t

DOH

Data Output Hold After CLK Rise

1.0

1.0

1.5

1.5

1.5

ns

t

CLZ

Clock to Low-Z

[14, 15, 16]

0

0

0

0

0

ns

t

CHZ

Clock to High-Z

[14, 15, 16]

2.6

2.8

3.5

4.0

4.5

ns

t

OEV

OE LOW to Output Valid

2.6

2.8

3.5

4.0

4.5

ns

t

OELZ

OE LOW to Output Low-Z

[14, 15, 16]

0

0

0

0

0

ns

t

OEHZ

OE HIGH to Output High-Z

[14, 15,

16]

2.6

2.8

3.5

4.0

4.5

ns

Set-up Times

t

AS

Address Set-up Before CLK Rise

1.2

1.2

1.5

1.5

1.5

ns

t

ALS

ADV/LD Set-up Before CLK Rise

1.2

1.2

1.5

1.5

1.5

ns

t

WES

GW, BW

X

Set-Up Before CLK Rise

1.2

1.2

1.5

1.5

1.5

ns

t

CENS

CEN Set-up Before CLK Rise

1.2

1.2

1.5

1.5

1.5

ns

t

DS

Data Input Set-up Before CLK Rise

1.2

1.2

1.5

1.5

1.5

ns

t

CES

Chip Enable Set-Up Before CLK

Rise

1.2

1.2

1.5

1.5

1.5

ns

Hold Times

t

AH

Address Hold After CLK Rise

0.3

0.5

0.5

0.5

0.5

ns

t

ALH

ADV/LD Hold after CLK Rise

0.3

0.5

0.5

0.5

0.5

ns

t

WEH

GW, BW

X

Hold After CLK Rise

0.3

0.5

0.5

0.5

0.5

ns

t

CENH

CEN Hold After CLK Rise

0.3

0.5

0.5

0.5

0.5

ns

t

DH

Data Input Hold After CLK Rise

0.3

0.5

0.5

0.5

0.5

ns

t

CEH

Chip Enable Hold After CLK Rise

0.3

0.5

0.5

0.5

0.5

ns

Notes:

13. This part has a voltage regulator internally; t

POWER

is the time that the power needs to be supplied above V

DD

minimum initially before a Read or Write operation

can be initiated.

14. t

CHZ

, t

CLZ

,t

OELZ

, and t

OEHZ

are specified with AC test conditions shown in part (b) of AC Test Loads. Transition is measured ± 200 mV from steady-state voltage.

15. At any given voltage and temperature, t

OEHZ

is less than t

OELZ

and t

CHZ

is less than t

CLZ

to eliminate bus contention between SRAMs when sharing the same

data bus. These specifications do not imply a bus contention condition, but reflect parameters guaranteed over worst case user conditions. Device is designed

to achieve tri-state prior to Low-Z under the same system conditions.

16. This parameter is sampled and not 100% tested.

17. Timing reference level is 1.5V when V

DDQ

= 3.3V and is 1.25V when V

DDQ

= 2.5V.

18. Test conditions shown in (a) of AC Test Loads unless otherwise noted.