Package diagrams, Continued) – Cypress CY7C1350G User Manual

Page 14

CY7C1350G

Document #: 38-05524 Rev. *F

Page 14 of 15

© Cypress Semiconductor Corporation, 2006. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be

used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its

products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

ZBT is a trademark of Integrated Device Technology, Inc. NoBL and No Bus Latency are trademarks of Cypress Semiconductor

Corporation. All product and company names mentioned in this document may be the trademarks of their respective holders.

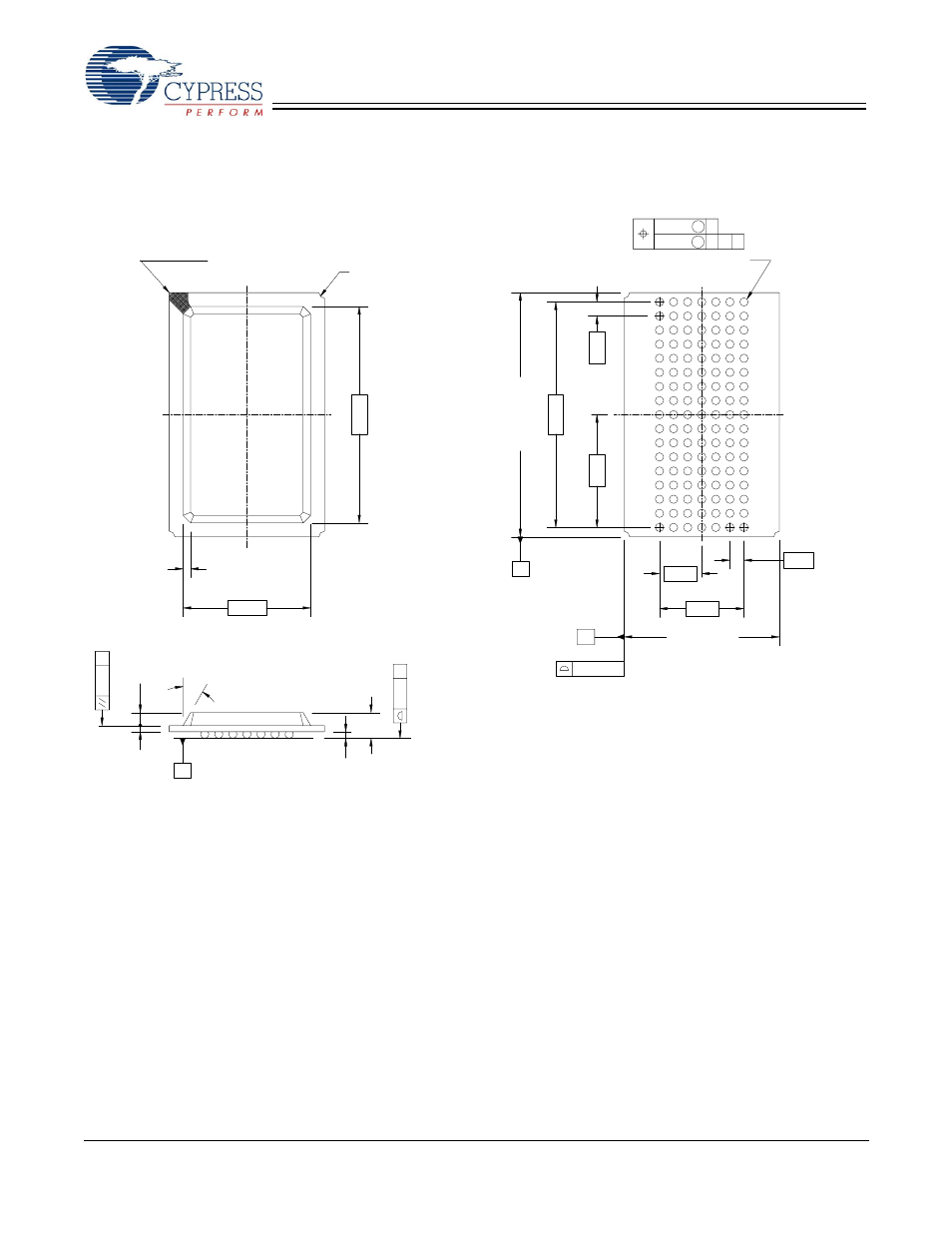

Package Diagrams

(continued)

1.27

20.32

2

1

6

5

4

3

7

L

E

A

B

D

C

H

G

F

K

J

U

P

N

M

T

R

12.00

19.50

30° TYP.

2.40

MAX.

A1 CORNER

0.70 REF.

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

A

B

2

1

4

3

6

5

7

Ø1.00(3X) REF.

7.62

22.00±0.20

14.00±0.20

1.27

6

0±0.10

C

0.15

C

B

A

0.15(4X)

Ø0.05 M C

Ø0.75±0.15(119X)

Ø0.25 M C A B

SEATING PLANE

0.90±0.05

3.81

10.16

0.25

C

0.56

51-85115-*B

119-Ball BGA (14 x 22 x 2.4 mm) (51-85115)