Dell PowerEdge 7250 User Manual

Page 32

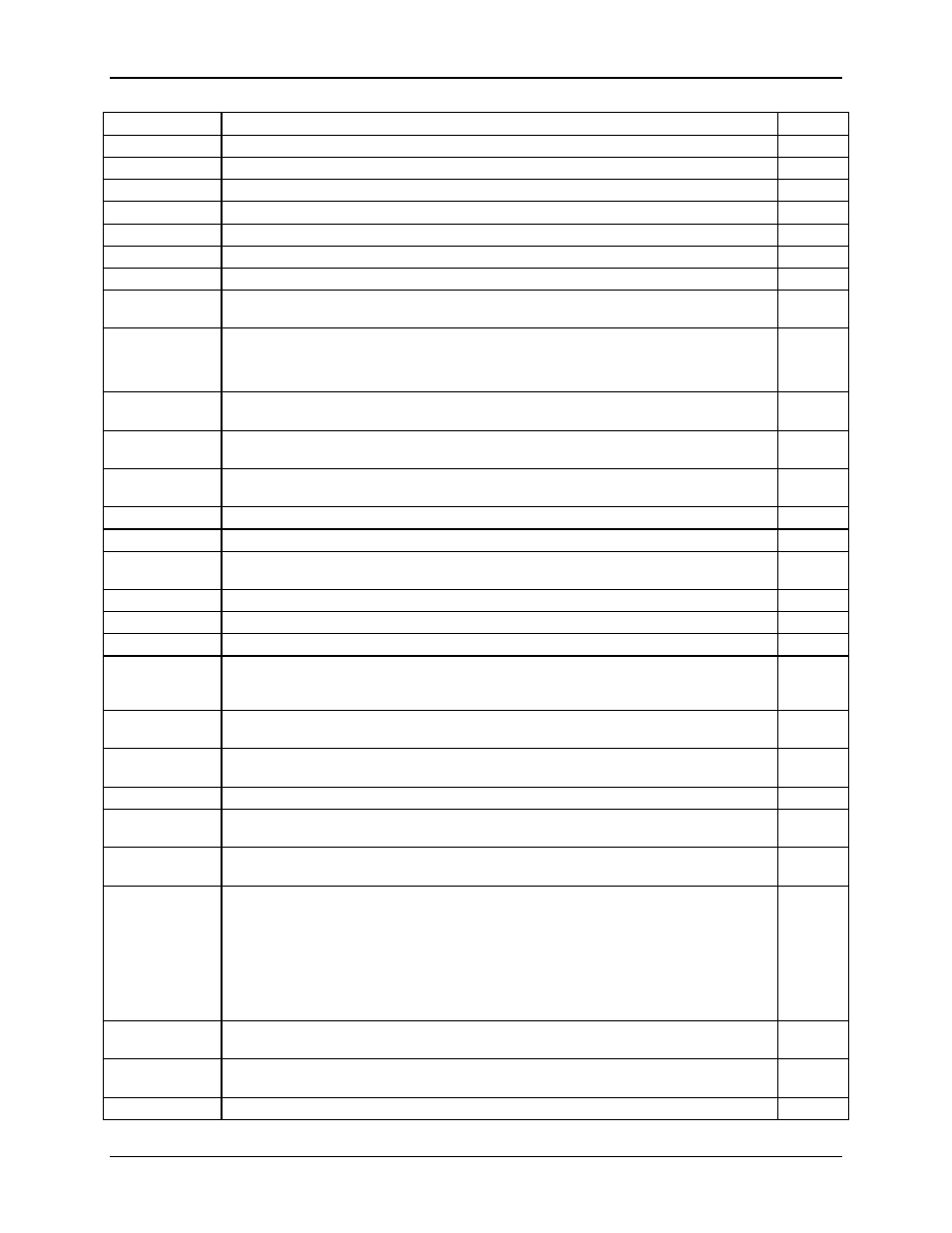

POST Codes

SR870BN4 Error Reference Guide

Revision

1.0

26

Code Value

Module

Display

0x00D7

Passing control to the interface module next.

South

0x00D8

The main system BIOS runtime code will be decompressed next.

South

0x00D9

Passing control to the main system BIOS in shadow RAM next.

South

0x0003

Next, checking for a soft reset or a power on condition.

South

0x0005

The BIOS stack has been built. Next, disabling cache memory.

South

0x0006

Uncompressing the POST code next.

South

0x0008

The CMOS checksum calculation is done next.

South

0x000B

Next, performing any required initialization before the keyboard BAT command is

issued.

South

0x000C

The keyboard controller input buffer is free. Next, issuing the BAT command to the

keyboard controller.

South

0x000E

The keyboard controller BAT command result has been verified. Next, performing any

necessary initialization after the keyboard controller BAT command test.

South

0x000F

The initialization after the keyboard controller BAT command test is done. The

keyboard command byte is written next.

South

0x0010

The keyboard controller command byte is written. Next, issuing the Pin 23 and 24

blocking and unblocking commands.

South

0x0011

Check for INS key pressed. Get POST info.

South

0x0012

Disable DMA controllers 1 and 2 and interrupt controllers 1 and 2.

South

0x0013

The video display has been disabled. Port B has been initialized. Next, initializing the

chipset.

South

0x0014

The 8254 timer test will begin next.

South

0x0019

The 8254 timer test is over. Starting the memory refresh test next.

South

0x001A

The memory refresh line is toggling. Check the 15-second on/off time next.

South

0x0023

Read the 8042 input-port and disable the MEGAKEY Green PC feature next. Make the

BIOS code segment writable and perform any necessary configuration before

initializing the interrupt vectors.

South

0x0024

The configuration required before interrupt vector initialization has completed. Interrupt

vector initialization is about to begin.

South

0x0025

Interrupt vector initialization is done. Clear the password if the POST DIAG switch is

on.

South

0x0027

Any initialization before setting video mode will be done next.

South

0x0028

Initialization before setting the video mode is complete. Configuring the monochrome

mode and color mode settings next.

South

0x002A

Bus initialization system, static, and output devices will be done next, if present.

Starting LAN redirection, displaying redirection console message.

South

Note that there

will be 15-bit

post codes in

this area. These

indicate Device

Initialization

Manager sub-

codes.

The convention for the DIM POST codes is as follows:

Port 80 = 0x2A

Port 81 = DIM Function number | DI number

South

0x002B

Passing control to the video ROM to perform any required configuration before the

video ROM test.

South

0x002C

All necessary processing before passing control to the video ROM is done. Look for the

video ROM next and pass control to it.

South

0x002D

The video ROM has returned control to BIOS POST. Perform any required processing

South