Dell PowerEdge 7250 User Manual

Page 25

SR870BN4 Error Reference Guide

POST Codes

Revision 1.0

19

Secret Decoder:

Bit 11:8 – 0xF stack-less code being executed, 0xD-0x0 – memory is available

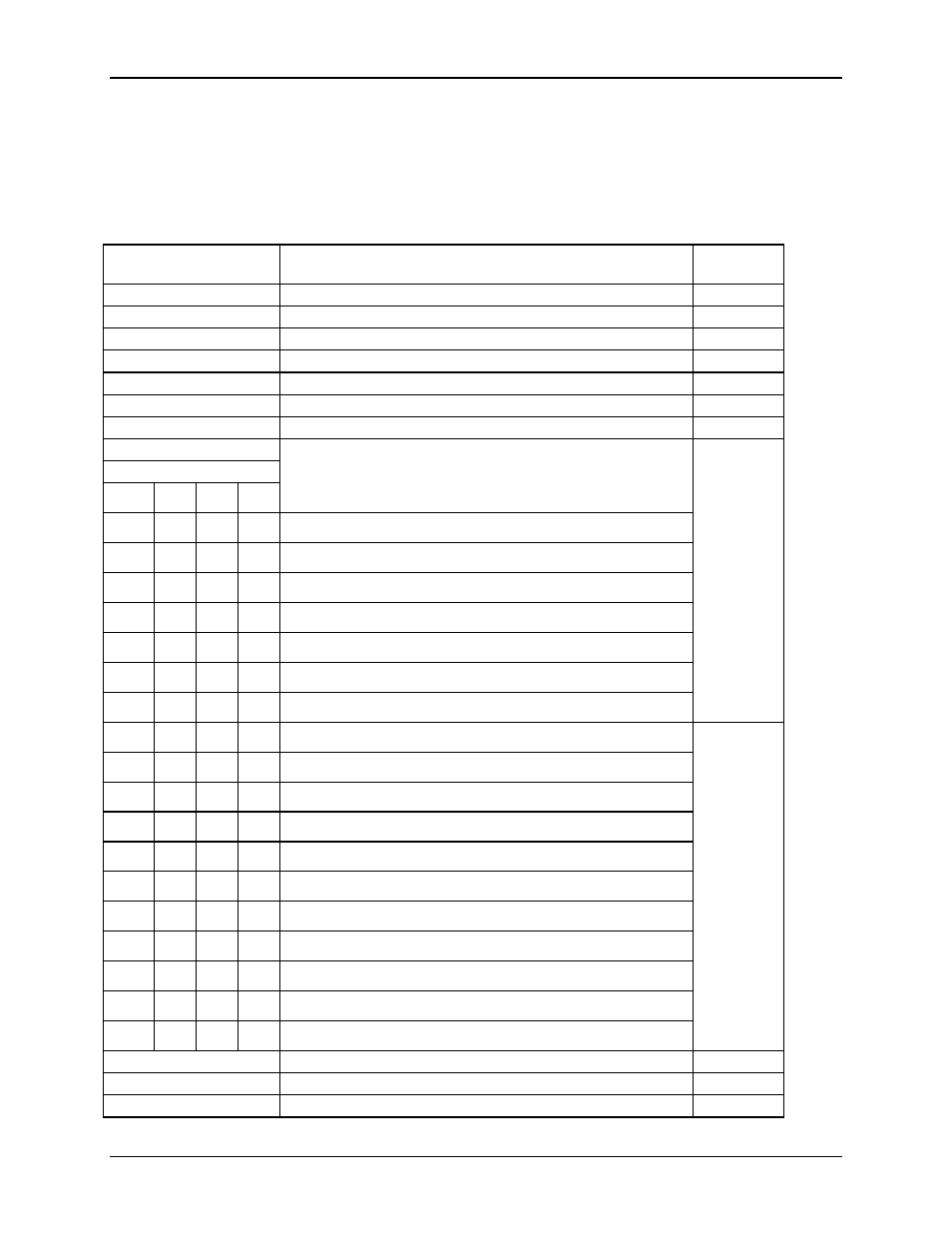

Table 5. General POST Code Module Numbers for Itanium™ – Based Platforms

Code Value (bit 8 = 1,

bits 11:4 shown below)

Module Display

0xFF Reserved

North

0xFE Reset

Condition

North

0xFD

Node BSP selection

North

0xFC

Early node init (SNCPEIM)

North

0xFB

Processor health/setup (CVDR PEIM)

North

0xFA

PAL/FW health status

North

0xF9-F7 Memory

Initialization

North

SUB MODULES

BITS

15:12 11:8 7:4 3:0

Memory Initialization

8 F

7

0

Pass1 Entry

8 F

7

1

RAC Initialization (Mem_DoRacInitialization())

8 F

7

2

Validate DIMMs (Mem_ValidateInstalledConfiguration())

8 F

7

3

Program MIRs/MITs (Mem_DoMirMitProgram())

8 F

7

4

Calculate CAS (Mem_CalcSysCas())

C F

7 4

Calculate CAS Error Loop

8 F

7

5

Program CAS (Mem_SetMrhdCasLatency())

North

8 F

7

6

Set Mrhd DIMM Geomentry (Mem_SetMrhdDimmGeometry())

8 F

7

7

Perform SLEW rate calibration (Mem_DoSlewRateCalibration)

8 F

7

8

Mem_InitDimmAndSetCasLatencyAndBurst()

8 F

7

9

DDR delay Calibration (Mem_DoDdrDelayCalibration())

8 F

8

0

DIMM path latency Calibration

8 F

8

1

DIMM Strobe Delay Calibration

8 F

8

2

Configure SNC timing

8 F

8

3

Set timings for write pattern

8 F

9

0

Levelization

8 F

9

8

Reconfigure memory

C F

9 F

Levelization failed. No Memory Found

0xF6 Memory

Test

North

0xF5 Platform

Discovery

North

0xF4-F3

SBSP selection & Platform Init

North