Cirrus Logic CS485xx User Manual

Page 68

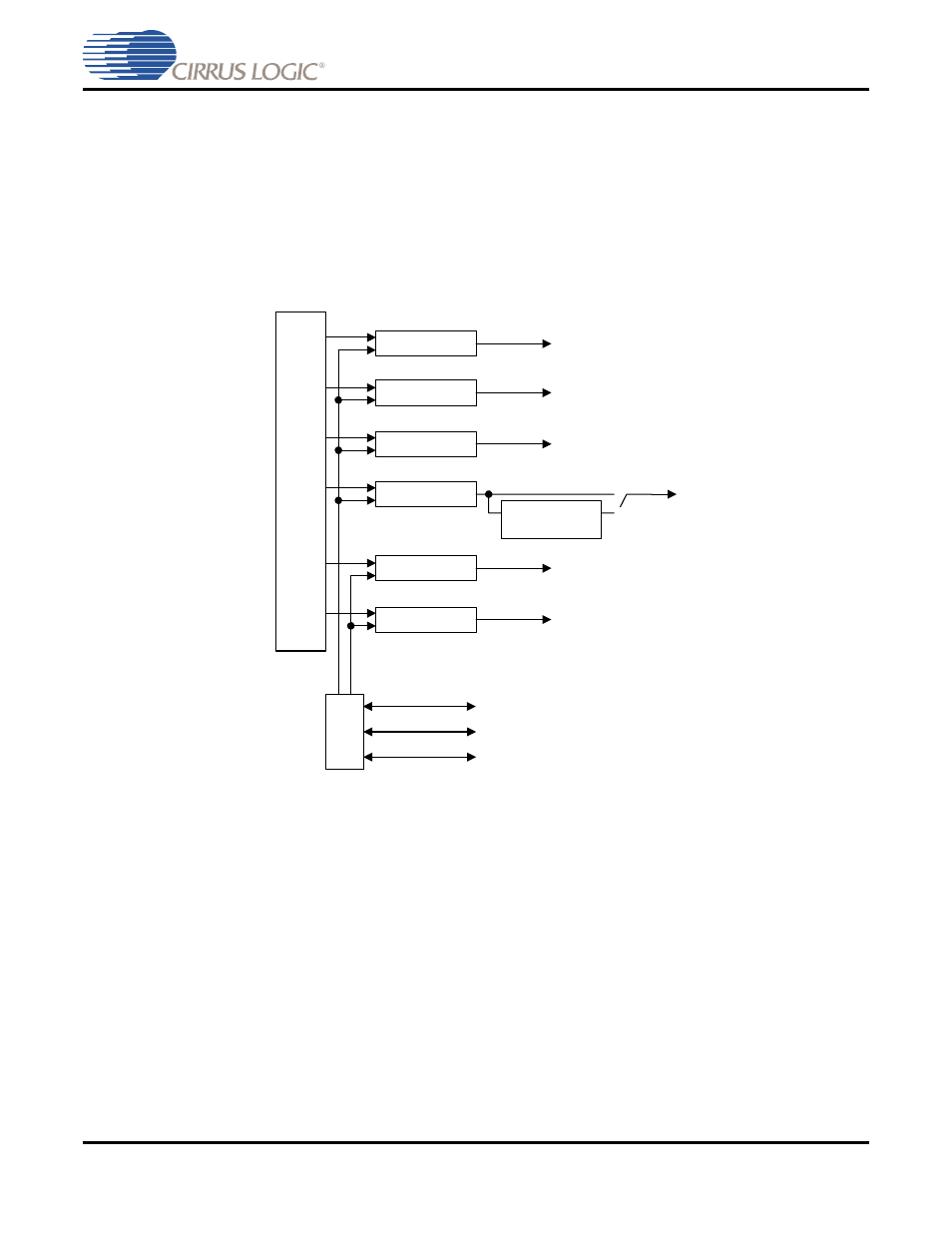

Digital Audio Output Port Description

CS485xx Hardware User’s Manual

DS734UM7

Copyright 2009 Cirrus Logic, Inc.

6-2

DAO_MCLK is the master clock and is firmware configurable to be either an input (slave) or an output

(master). If MCLK is to be used as an output, the internal PLL must be used. As an output MCLK can be

configured to provide a 128Fs, 256Fs, or 512Fs clock, where Fs is the output sample rate.

•

DAO_SCLK is the bit clock used to clock data out on DAOn_DATA[n].

•

DAO_LRCLK is the data framing clock whose frequency is equal to the sampling frequency for the

DAO data outputs.

•

DAOn_DATA[n] are the data outputs and are typically configured for outputting two channels of I

2

S

or left-justified PCM data.

.

Figure 6-1. CS48560 DAO Block Diagram

DAO1_DATA0

P

e

ri

ph

er

a

l B

u

s

to

D

M

A

DAO1_DATA1

DAO1_DATA2

DAO1_DATA3

DAO1_DATA3, XMTA

DAO2_DATA0

DAO2_DATA1

Cl

oc

k

M

a

na

ge

r

DAO_MCLK

DAO_SCLK

DAO_LRCLK

SPDIF

ENCODER

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)