3 spi port, C stop condition or an i, C repeated-start condition occurs – Cirrus Logic CS485xx User Manual

Page 45

3-13

Copyright 2009 Cirrus Logic, Inc.

DS734UM7

SPI Port

CS485xx Hardware User’s Manual

If there are more data words to read, IRQ will fall at the rising edge of CLK for the NACK. Otherwise, IRQ

remains high until an I

2

C Stop condition or an I

2

C Repeated-Start condition occurs.

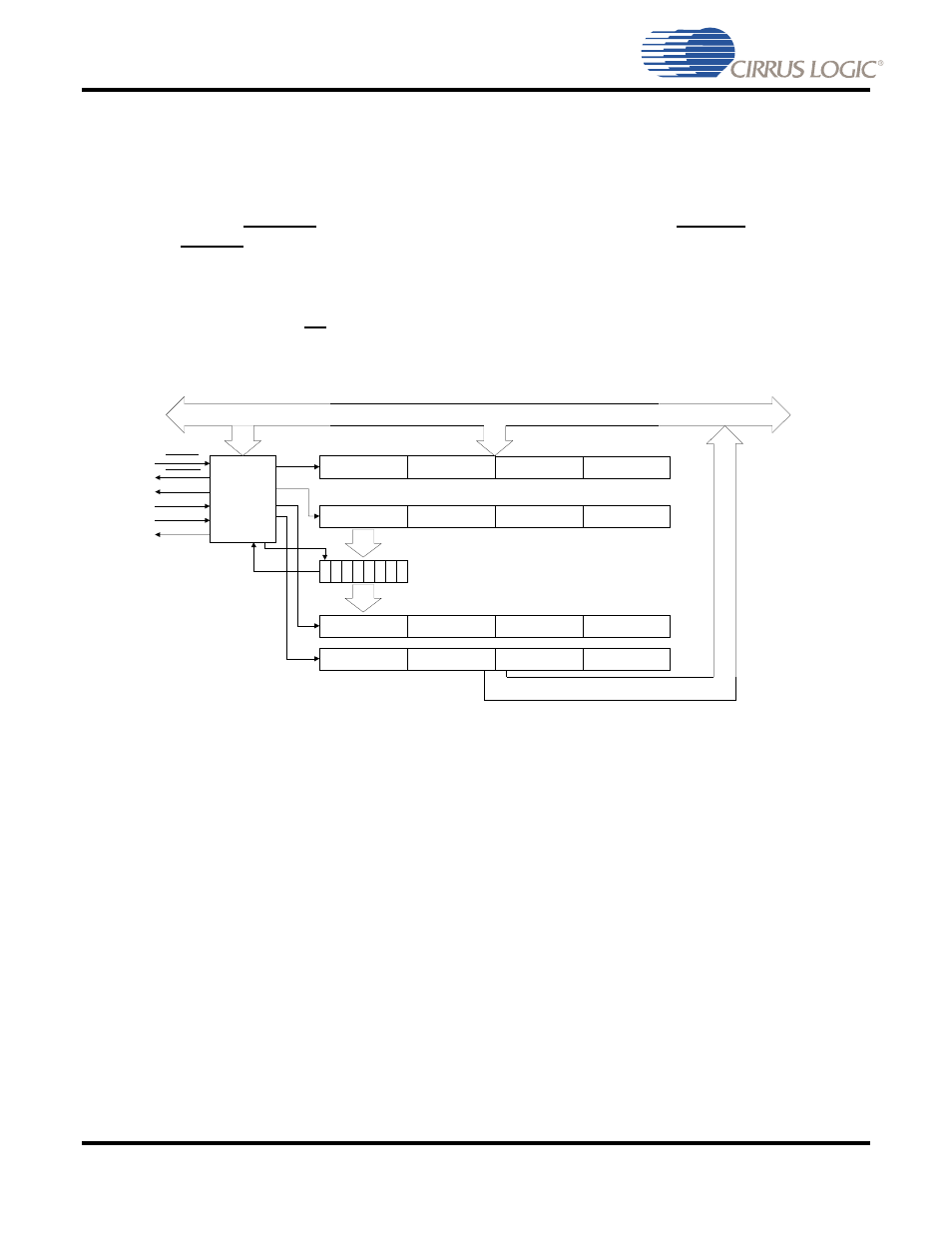

3.3 SPI Port

The CS485xx Serial Peripheral Interface (SPI) bus has been developed for 8-bit digital control applications,

such as those requiring microcontrollers. SPI communication is accomplished with 6 lines: Serial Control

Port Input Busy (SCP_BSY), Serial Control Port Data Ready Interrupt Request (SCP_IRQ), Serial Chip

Select (SCP_CS), Serial Control Clock (SCP_CLK), Master Out/Slave In data (SCP_MOSI), and a Master

In/Slave Out data (SCP_MISO). Although the separate data I/O lines provide full-duplex capabilities, the

CS485xx chip only uses a half-duplex SPI-bus. Each device on the bus may respond to one or more unique

commands, and can operate as either a transmitter or receiver. A device is considered the master in a

transaction if it drives the CS pin of another device, and is also mastering the SCP_CLK line. A block

diagram of the CS485xx SPI Serial Control Port is provided in

Figure 3-12

.

Figure 3-12. SPI Serial Control Port Internal Block Diagram

Table 3-2

shows the signal names, descriptions, and pin number of the signals associated with the SPI

Serial Control Port on the CS485xx.

SPI Control /

Clocking

SCP_BSY

SCP_IRQ

LSB (Byte 0)

Byte 1

Byte2

MSB (Byte 3)

LSB (Byte 0)

Byte 1

Byte2

MSB (Byte 3)

MSB (Byte 3)

Byte 2

Byte1

LSB (Byte 0)

MSB (Byte 3)

Byte 2

Byte1

LSB (Byte 0)

7

6

5

4

3

2

1

0

Internal Bus

SCP_CLK

SCP_MOSI

SCP_MISO

SCP_CS