2 clock and data flow for s/pdif input, 2 clock and data flow for s/pdif input -15, Figure 1-9. s/pdif clocking -15 – Cirrus Logic CDB470xx User Manual

Page 22

1-15

Copyright 2014 Cirrus Logic, Inc.

DS886DB11

Audio Clocking

CDB47xxx User’s Manual

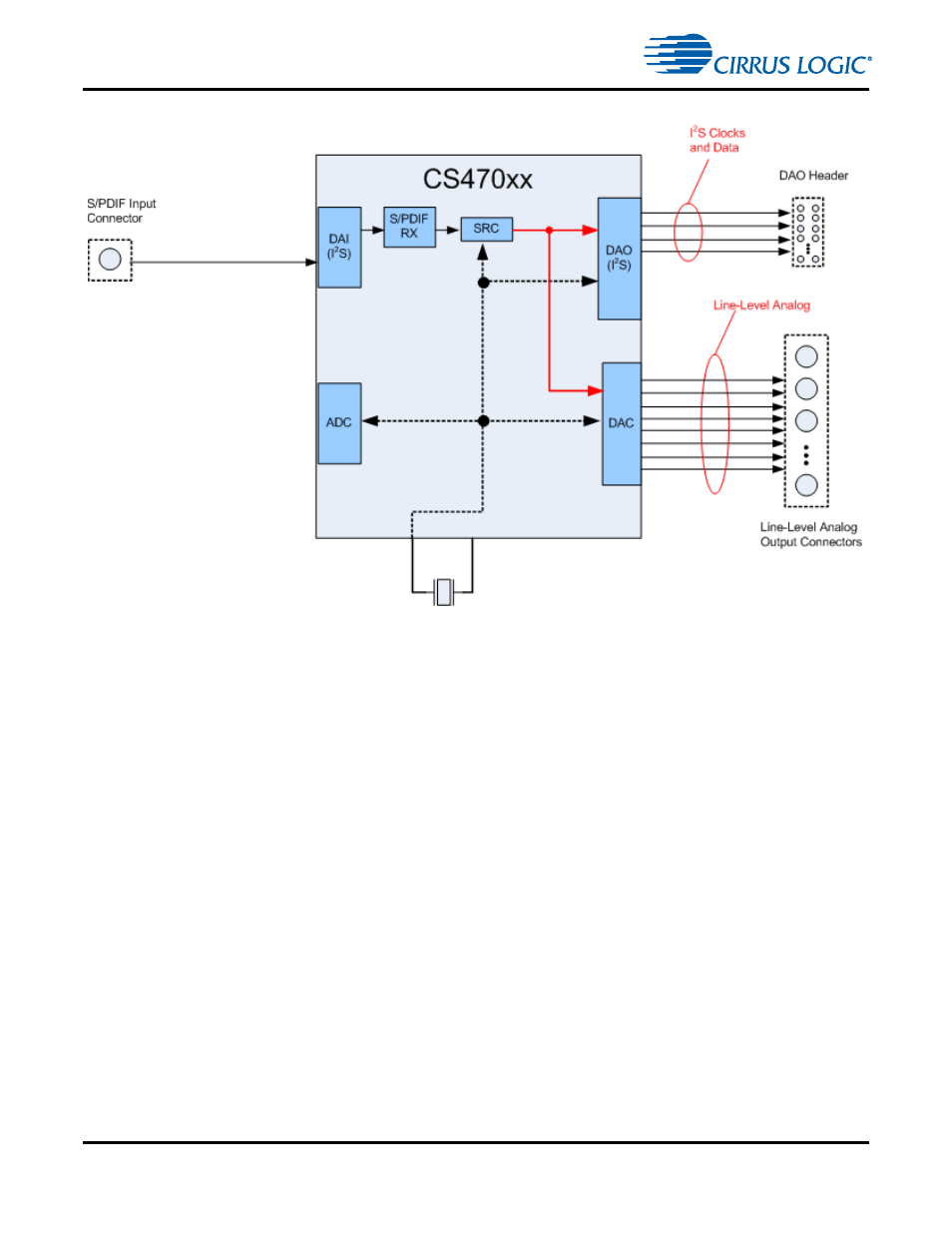

1.5.2 Clock and Data Flow for S/PDIF Input

Figure 1-9. S/PDIF Clocking

The S/PDIF clocking architecture is used when any S/PDIF RX is used as an audio source, whether from

the optical RX, coaxial RX, or brought in on the DAI header.

illustrates this clocking

configuration.

The incoming S/PDIF stream is always rate matched to another MCLK in the system through an SRC.

This means that the DAO can be run at a constant Fs that is independent of the incoming S/PDIF Fs. This

is useful in systems with digital amplifiers and wireless audio transmitter modules that requires a fixed Fs.

The CS470xx can master its output clocks, or slave to clocks from another source.

See also other documents in the category Cirrus Logic Hardware:

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)