Table 3. digital interface format - dif1 and dif0, Table 4. de-emphasis control – Cirrus Logic CS4224 User Manual

Page 21

CS4223 CS4224

DS290F1

21

SDIN

9

Serial Data Input (Input) - Two's complement MSB-first serial data is input on this pin. The

required relationship between the left/right clock, serial clock and serial data is defined by the

DIF1-0 pins. The options are detailed in Figures 8 - 11.

DIF0, DIF1

10,11

Digital Interface Format (Input) - The required relationship between the left/right clock, serial

clock and serial data is defined by the Digital Interface Format. The options are detailed in Fig-

ures 8 - 11.

DEM0, DEM1

12,18

De-Emphasis Select (Input) - Controls the activation of the standard 50/15 µs de-emphasis

filter. 32, 44.1, or 48 kHz sample rate selection defined in Table 4.

VL

13

Digital Logic Power (Input) - Positive power supply for the digital interface section. Typically

3.0 to 5.0 VDC.

AINR-, AINR+

16,17

Differential Right Channel Analog Input (Input) - The full scale analog input level (differen-

tial) is specified in the Analog Characteristics specification table and may be AC coupled or DC

coupled into the device, see Figure 12 for optional line input buffer.

AINL-, AINL+

19,20

Differential Left Channel Analog Input (Input) - The full scale analog input level (differential)

is specified in the Analog Characteristics specification table and may be AC coupled or DC

coupled into the device, see Figure 12 for optional line input buffer.

VA

21

Analog Power (Input) - Positive power supply for the analog section. Nominally +5 Volts.

AGND

22

Analog Ground (Input) - Analog ground reference.

AOUTR-,

AOUTR+

23, 24

Differential Right Channel Analog Output (Output) - The full scale analog output level (dif-

ferential) is specified in the Analog Characteristics specification table.

AOUTL-,

AOUTL+

25, 26

Differential Left Channel Analog Output (Output) - The full scale analog output level (differ-

ential) is specified in the Analog Characteristics specification table.

RST

27

Reset (Input) - When low, the device enters a low power mode and all internal registers are

reset, including the control port. When high, the control port becomes operational and normal

operation will occur.

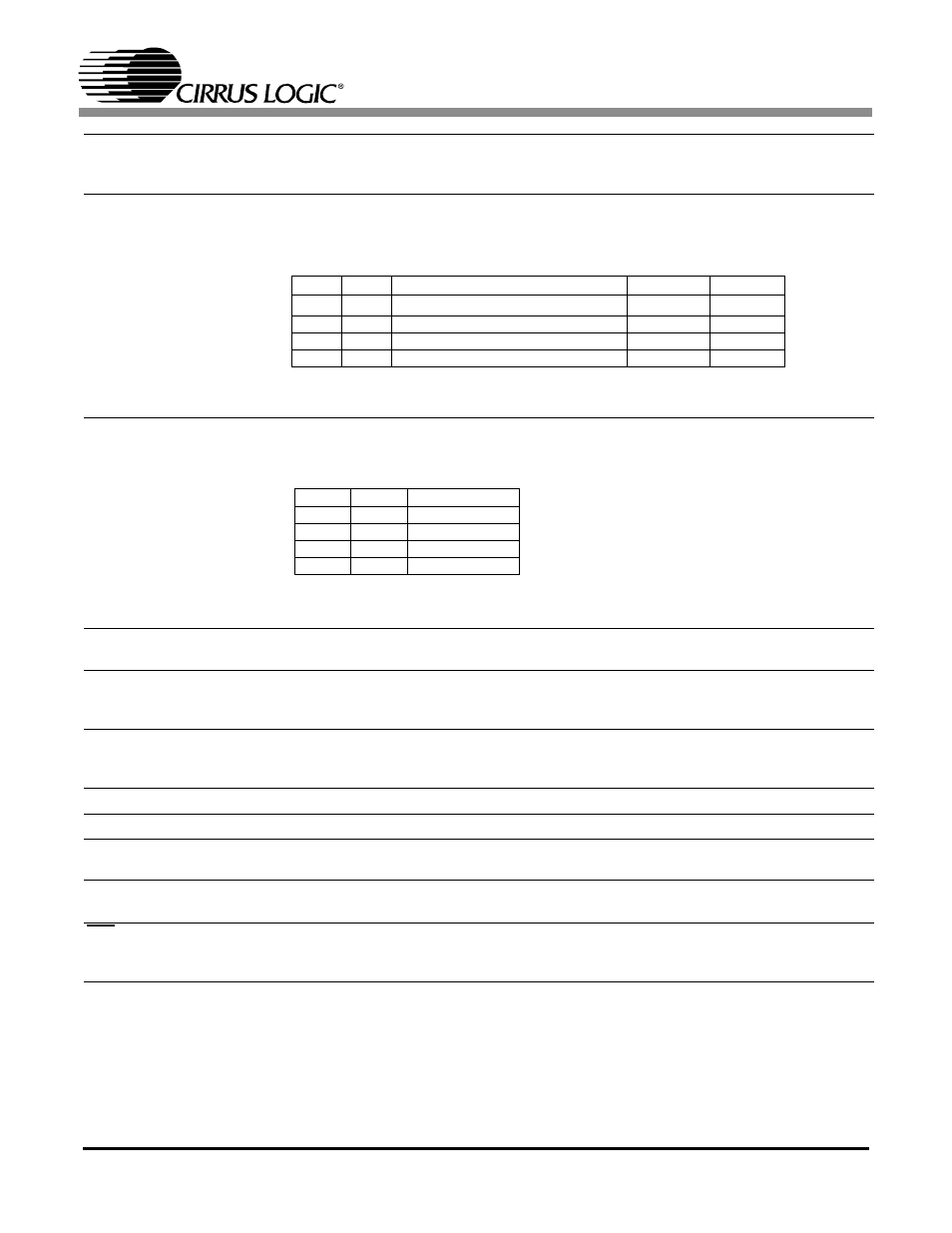

DIF1

DIF0

DESCRIPTION

FORMAT

FIGURE

0

0

I

2

S, up to 24-bit data

0

0

1

Left Justified, up to 24-bit data

1

1

0

Right Justified, 24-bit Data

2

1

1

Right Justified, 20-bit Data

3

Table 3. Digital Interface Format - DIF1 and DIF0

DEM0

DEM1

De-Emphasis

0

0

32 kHz

0

1

44.1 kHz

1

0

48 kHz

1

1

Disabled

Table 4. De-emphasis Control