1 master clock control (mck), 7 master clock control (address 07h) – Cirrus Logic CS4224 User Manual

Page 19

CS4223 CS4224

DS290F1

19

5.6

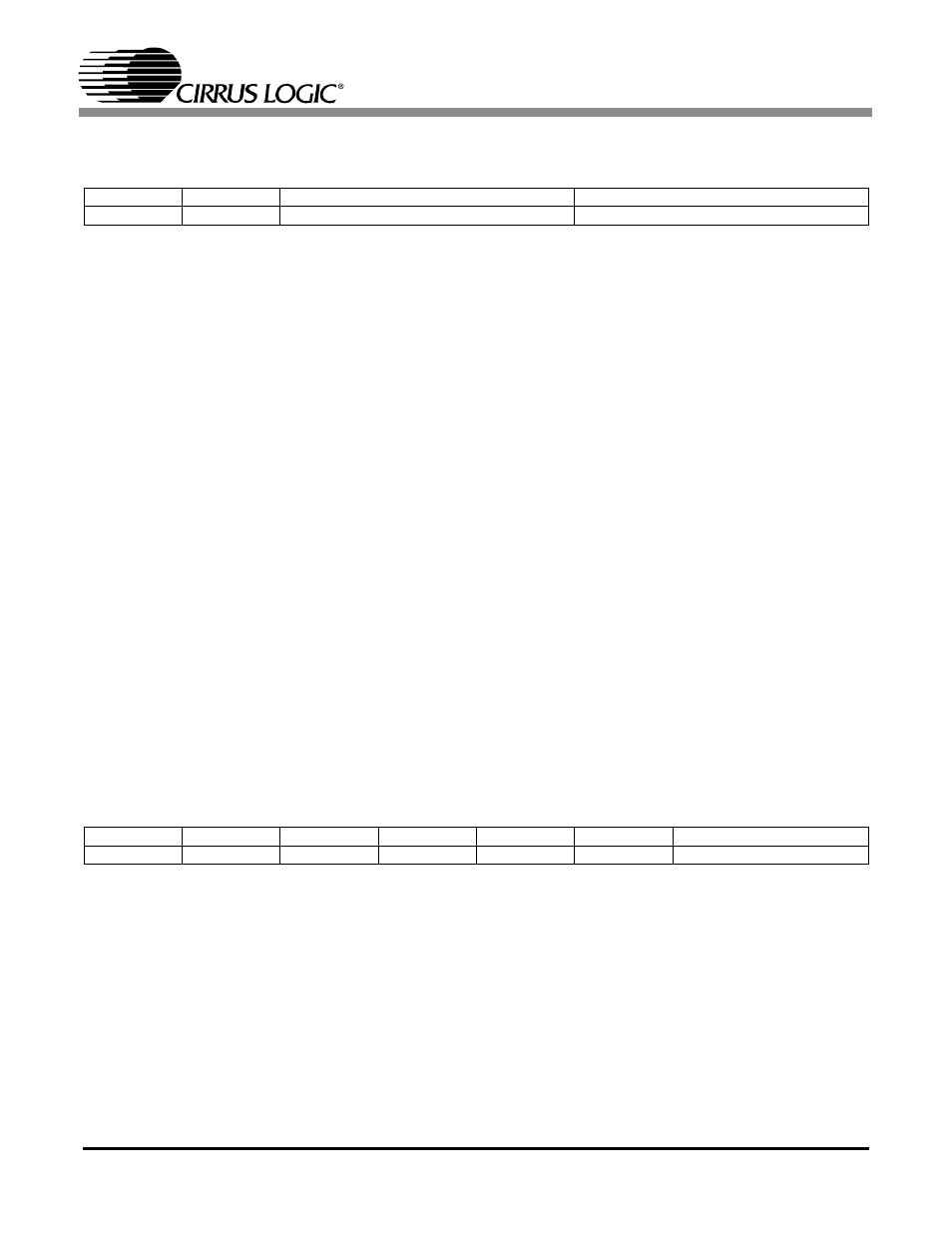

Converter Status Report (Read Only) (address 06h)

5.6.1

LEFT AND RIGHT CHANNEL ACCEPTANCE BIT (ACCR-ACCL)

Default = 0

0 - Requested setting valid

1 - New setting loaded

Function:

The ACCR and ACCL bits indicate when a change in the Output Attenuator Level has occurred for

the left and right channels, respectively. The value will be high when a new setting is loaded into the

Output Attenuator Level registers. The value will return low when the requested attenuation setting

has taken effect.

5.6.2

LEFT AND RIGHT CHANNEL ADC OUTPUT LEVEL (LVR AND LVL)

Default = 000

000 - Normal output levels

001 - -6 dB level

010 - -5 dB level

011 - -4 dB level

100 - -3 dB level

101 - -2 dB level

110 - -1 dB level

111 - Clipping

Function:

The analog-to-digital converter is continually monitoring the peak digital signal output for both the left

and right channel, prior to the digital limiter. The maximum output value is stored in the LVL and LVR

bits. The LVL and LVR bits are ‘sticky’, so they are reset after each read is performed.

5.7

Master Clock Control (address 07h)

5.7.1

MASTER CLOCK CONTROL (MCK)

Default = 00

00 - XTI = 256 Fs for Master Mode

01 - XTI = 384 Fs for Master Mode

10 - XTI = 512 Fs for Master Mode

Function:

The MCK bits allow for control of the Master Clock, XTI, input frequency.

Note: These bits are not valid when operating in slave mode.

7

6

5

4

3

2

1

0

ACCR

ACCL

LVR2

LVR1

LVR0

LVL2

LVL2

LVL0

0

0

0

0

0

0

0

0

7

6

5

4

3

2

1

0

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

MCK1

MCK0

0

0

0

0

0

0

0

0