Adsp-2181, Rev. 0 –14, Pd × θ – Analog Devices ADSP-2181 User Manual

Page 14: Thermal resistance (case-to-ambient) θ, Thermal resistance (junction-to-ambient) θ, Thermal resistance (junction-to-case) package θ, The application operates at v, 0 v and t, 30 ns. total power dissipation = p, C × v

ADSP-2181/ADSP-2183

REV. 0

–14–

ADSP-2181

ENVIRONMENTAL CONDITIONS

Ambient Temperature Rating:

T

AMB

= T

CASE

– (PD

×

θ

CA

)

T

CASE

= Case Temperature in

°

C

PD = Power Dissipation in W

θ

CA

= Thermal Resistance (Case-to-Ambient)

θ

JA

= Thermal Resistance (Junction-to-Ambient)

θ

JC

= Thermal Resistance (Junction-to-Case)

Package

θ

JA

θ

JC

θ

CA

TQFP

50

°

C/W

2

°

C/W

48

°

C/W

PQFP

41

°

C/W

10

°

C/W

31

°

C/W

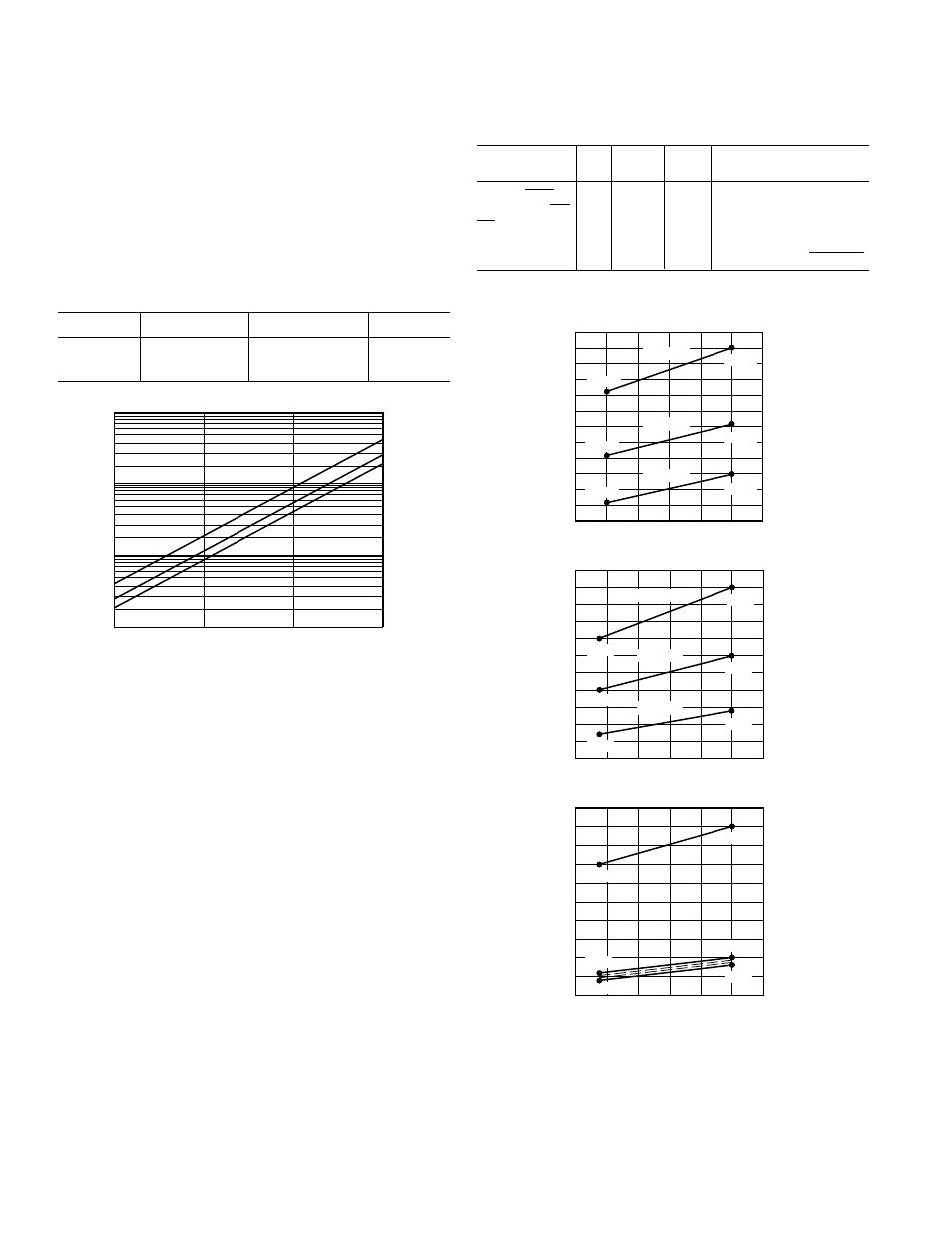

TEMPERATURE –

°

C

CURRENT (LOG SCALE) – µA

1000

100

0

–5

85

25

55

10

V

DD

= 5.5V

V

DD

= 5.0V

V

DD

= 4.5V

NOTES:

1. REFLECTS ADSP-2181 OPERATION IN LOWEST POWER MODE.

(SEE "SYSTEM INTERFACE" CHAPTER OF THE ADSP-2100 FAMILY

USER'S MANUAL FOR DETAILS.)

2. CURRENT REFLECTS DEVICE OPERATING WITH NO OUTPUT LOADS.

Figure 8. Power-Down Supply Current (Typical)

POWER DISSIPATION

To determine total power dissipation in a specific application,

the following equation should be applied for each output:

C

×

V

DD

2

×

f

C = load capacitance, f = output switching frequency.

Example:

In an application where external data memory is used and no

other outputs are active, power dissipation is calculated as

follows:

Assumptions:

•

External data memory is accessed every cycle with 50% of the

address pins switching.

•

External data memory writes occur every other cycle with

50% of the data pins switching.

•

Each address and data pin has a 10 pF total load at the pin.

•

The application operates at V

DD

= 5.0 V and t

CK

= 30 ns.

Total Power Dissipation = P

INT

+ (C

×

V

DD

2

×

f )

P

INT

= internal power dissipation from Power vs. Frequency

graph (Figure 9).

(C

×

V

DD

2

×

f ) is calculated for each output:

# of

Pins

×

C

×

V

DD

2

×

f

Address, DMS

8

×

10 pF

×

5

2

V

×

33.3 MHz

=

66.6 mW

Data Output, WR 9

×

10 pF

×

5

2

V

×

16.67 MHz =

37.5 mW

RD

1

×

10 pF

×

5

2

V

×

16.67 MHz =

4.2 mW

CLKOUT

1

×

10 pF

×

5

2

V

×

33.3 MHz

=

8.3 mW

116.6 mW

Total power dissipation for this example is P

INT

+ 116.6 mW.

1/t

CK

– MHz

POWER (P

INT

) – mW

570

450

360

28

34

29

30

31

32

33

550

480

420

390

530

510

330

300

270

240

2181 POWER, INTERNAL

V

DD

= 5.5V

V

DD

= 5.0V

V

DD

= 4.5V

550mW

425mW

330mW

490mW

365mW

275mW

1/f

CK

– MHz

95

60

45

28

34

29

30

31

32

33

90

65

55

50

85

75

80

70

40

POWER, IDLE

1, 2

POWER (P

IDLE

) – mW

90mW

70mW

54mW

47mW

60mW

75mW

V

DD

= 5.5V

V

DD

= 5.0V

V

DD

= 4.5V

1/f

CK

– MHz

75

40

30

28

34

29

30

31

32

33

70

45

35

65

55

60

50

25

POWER, IDLE

n MODES

3

70mW

35mW

33mW

29mW

31mW

60mW

IDLE;

IDLE (16)

IDLE (128)

POWER (P

IDLE

n

) – mW

VALID FOR ALL TEMPERATURE GRADES.

1

POWER REFLECTS DEVICE OPERATING WITH NO OUTPUT LOADS.

2

IDLE REFERS TO ADSP-2181 STATE OF OPERATION DURING EXECUTION OF IDLE

INSTRUCTION. DEASSERTED PINS ARE DRIVEN TO EITHER V

DD

OR GND.

3

TYPICAL POWER DISSIPATION AT 5.0V V

DD

DURING EXECUTION OF IDLE

n

INSTRUCTION (CLOCK FREQUENCY REDUCTION).

4

I

DD

MEASUREMENT TAKEN WITH ALL INSTRUCTIONS EXECUTING FROM INTERNAL

MEMORY. 50% OF THE INSTRUCTIONS ARE MULTIFUNCTION (TYPES 1,4,5,12,13,14),

30% ARE TYPE 2 AND TYPE 6, AND 20% ARE IDLE INSTRUCTIONS.

Figure 9. Power vs. Frequency