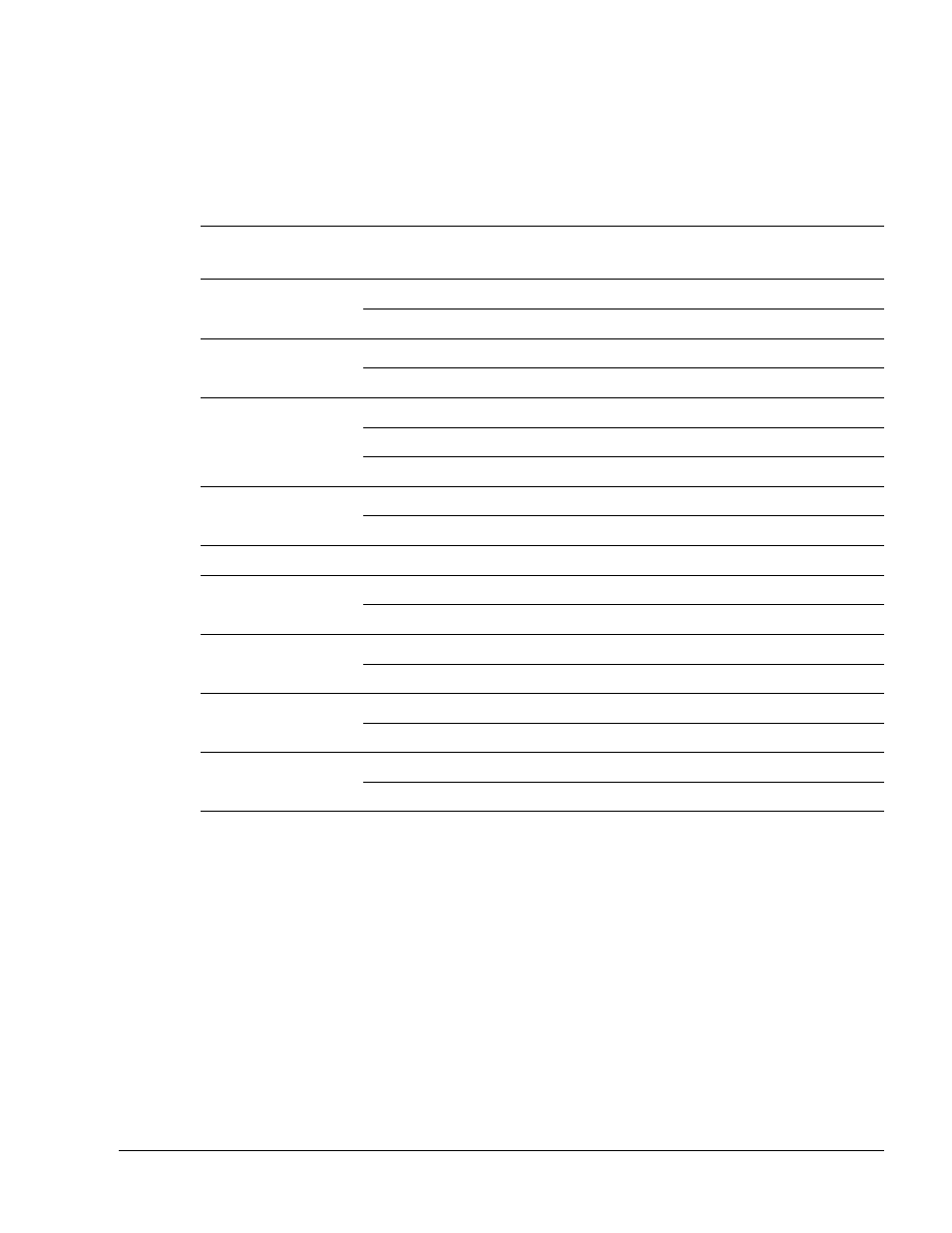

9 branches, Branches -15, Table 14-10 – ARM Cortex R4F User Manual

Page 379: Branch instruction cycle timing behavior -15

Cycle Timings and Interlock Behavior

ARM DDI 0363E

Copyright © 2009 ARM Limited. All rights reserved.

14-15

ID013010

Non-Confidential, Unrestricted Access

14.9

Branches

This section describes the cycle timing behavior for the

B

,

BL

,

BLX

,

BX

,

BXJ

,

CBNZ

,

CBZ

,

TBB

, and

TBH

instructions. Branches are subject to dynamic and return stack predictions. Table 14-10 shows

example branch instructions and their cycle timing behavior.

Table 14-10 Branch instruction cycle timing behavior

Example instruction

Cycles

Memory

cycles

Comments

B

BLX

a

1

-

Correct dynamic prediction

8

-

Incorrect dynamic prediction

BX

b

1

-

Correct return stack prediction

9

-

Incorrect return stack prediction

BX

b

1

-

Correct condition prediction and correct return stack prediction

8

-

Incorrect condition prediction

9

-

Correct condition prediction and incorrect return stack prediction

BXJ

1

-

Condition code fails

9

-

Condition code passes

BLX

9

-

-

BLX

1

-

Condition code fails

9

-

Condition code passes

CBZ

,

CBNZ

1

-

Correct condition prediction

8

-

Incorrectly predicted

TBB [

c

9

1

Condition code fails

9

1

Condition code passes

TBH [

9

1

Condition code fails

9

1

Condition code passes

a. Return stack push.

b. Return stack pop, if condition passes.

c.

and

are Very Early Regs.