1 floating-point system id register, fpsid, Table 12-3, Fpsid register bit functions -5 – ARM Cortex R4F User Manual

Page 346: Figure 12-2, Floating-point system id register format -5

FPU Programmer’s Model

ARM DDI 0363E

Copyright © 2009 ARM Limited. All rights reserved.

12-5

ID013010

Non-Confidential, Unrestricted Access

Note

All hardware ID information is privileged access only:

FPSID is privileged access only

This is a change in VFPv3 compared to VFPv2.

MVFR registers are privileged access only

User code must issue a system call to determine the features that are supported.

The following sections describe the VFP system registers:

•

Floating-Point System ID Register, FPSID

•

Floating-Point Status and Control Register, FPSCR on page 12-6

•

Floating-Point Exception Register, FPEXC on page 12-7

•

Media and VFP Feature Registers, MVFR0 and MVFR1 on page 12-8.

12.3.1

Floating-Point System ID Register, FPSID

The FPSID Register is a read-only register that must be accessed in Privileged mode only. It

indicates which VFP implementation is being used.

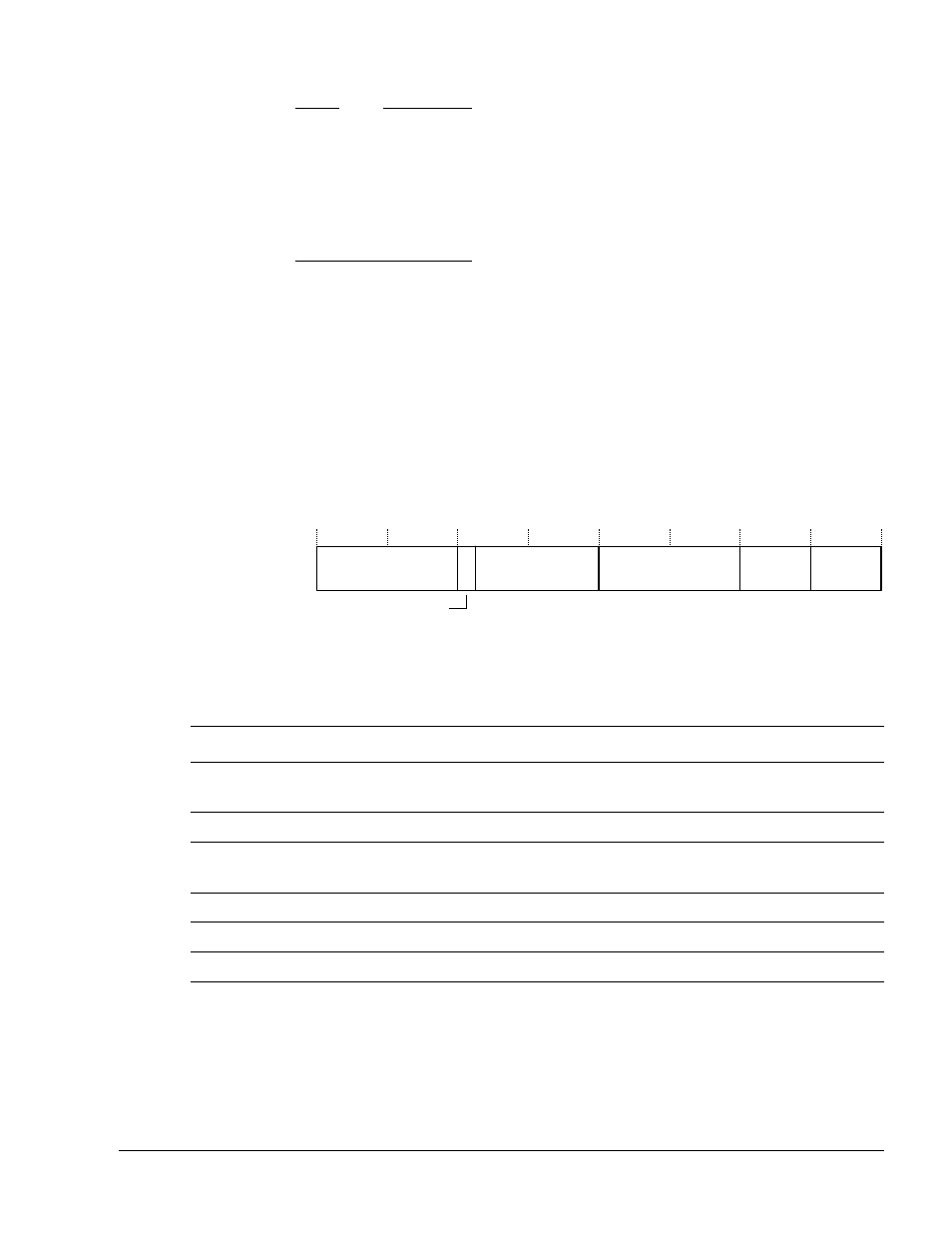

Figure 12-2 shows the bit arrangement of the FPSID Register.

Figure 12-2 Floating-Point System ID Register format

Table 12-3 shows how the bit values correspond with the FPSID Register functions.

HW

Sub architecture

Variant

Revision

4

Implementer

Part number

31

24 23 22

16 15

8 7

4 3

0

Table 12-3 FPSID Register bit functions

Bits

Field

Function

[31:24]

Implementer

ARM Limited:

0x41

= A

[23]

Hardware or software

0 = hardware implementation

[22:16]

Subarchitecture version

VFP architecture v3 or later with Common VFP subarchitecture v2

a

:

0x02

[15:8]

Part number

0x31

= Cortex-R4F

[7:4]

Variant

0x4

= Cortex-R4F

[3:0]

Revision

See Product revision information on page 1-24 for details of the value of this field.

a. For details of the Common VFP subarchitecture see the ARM Architecture Reference Manual.