6 c0, multiprocessor id register, 7 the processor feature registers, Figure 4-11 – ARM Cortex R4F User Manual

Page 102: Multiprocessor id register format -18, Figure 4-12, Processor feature register 0 format -18

System Control Coprocessor

ARM DDI 0363E

Copyright © 2009 ARM Limited. All rights reserved.

4-18

ID013010

Non-Confidential, Unrestricted Access

MRC p15, 0,

4.2.6

c0, Multiprocessor ID Register

The Multiprocessor ID Register enables cores to be recognized and characterized within a

multiprocessor system.

The Multiprocessor ID Register is:

•

read-only register

•

accessible in Privileged mode only.

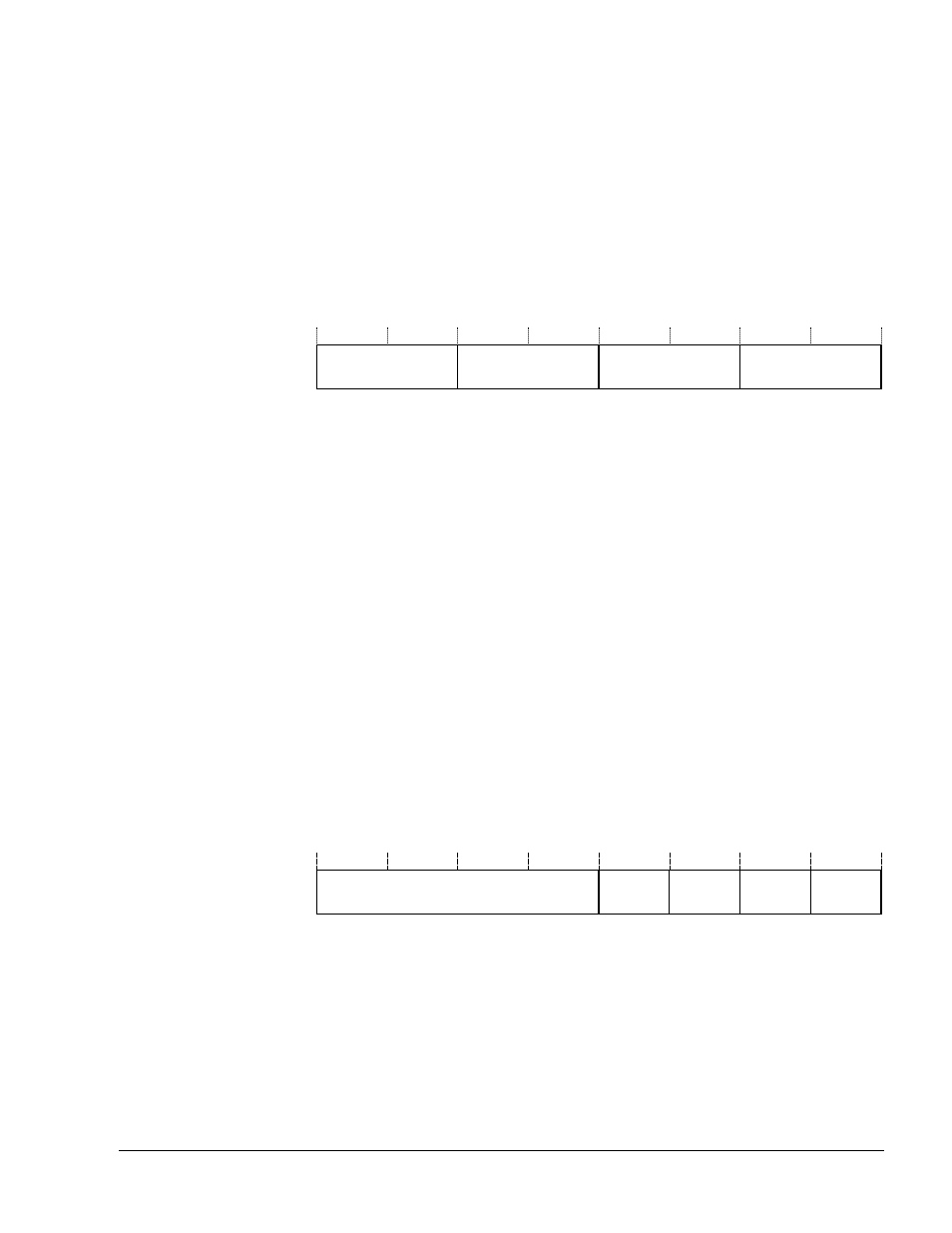

Figure 4-11 shows the arrangement of bits in the register.

Figure 4-11 Multiprocessor ID Register format

Because this is a uniprocessor system, this register is Read-As-Zero.

To access the Multiprocessor ID Register, read CP15 with:

MRC p15, 0,

4.2.7

The Processor Feature Registers

There are two Processor Feature Registers, PFR0 and PFR1. This section describes:

•

c0, Processor Feature Register 0, PFR0

•

c0, Processor Feature Register 1, PFR1 on page 4-19.

c0, Processor Feature Register 0, PFR0

The Processor Feature Register 0 provides information about the execution state support and

programmer’s model for the processor.

Processor Feature Register 0 is:

•

a read-only register

•

accessible in Privileged mode only.

Figure 4-12 shows the bit arrangement for Processor Feature Register 0.

Figure 4-12 Processor Feature Register 0 format

Affinity Level 2

Reserved

31

16

8 7

0

Affinity Level 0

Affinity Level 1

24 23

Reserved

State3

31

16 15

8 7

3

0

State2

State1

State0

4

11

12