28 validation registers, Table 4-42, Nval irq enable set register bit functions -62 – ARM Cortex R4F User Manual

Page 146: Figure 4-44, Nval irq enable set register format -62

System Control Coprocessor

ARM DDI 0363E

Copyright © 2009 ARM Limited. All rights reserved.

4-62

ID013010

Non-Confidential, Unrestricted Access

4.2.28

Validation Registers

The processor implements a set of validation registers. This section describes:

•

c15, nVAL IRQ Enable Set Register

•

c15, nVAL FIQ Enable Set Register on page 4-63

•

c15, nVAL Reset Enable Set Register on page 4-64

•

c15, nVAL Debug Request Enable Set Register on page 4-64

•

c15, nVAL IRQ Enable Clear Register on page 4-65

•

c15, nVAL FIQ Enable Clear Register on page 4-66

•

c15, nVAL Reset Enable Clear Register on page 4-67

•

c15, nVAL Debug Request Enable Clear Register on page 4-68

•

c15, nVAL Cache Size Override Register on page 4-69.

c15, nVAL IRQ Enable Set Register

The nVAL IRQ Enable Set Register enables any of the PMC Registers, PMC0-PMC2, and

CCNT, to generate an interrupt request on overflow. If enabled, the interrupt request is signaled

by nVALIRQ being asserted LOW.

The nVAL IRQ Enable Set Register is:

•

A read/write register.

•

Always accessible in Privileged mode. The USEREN Register determines access, see c9,

User Enable Register on page 6-15.

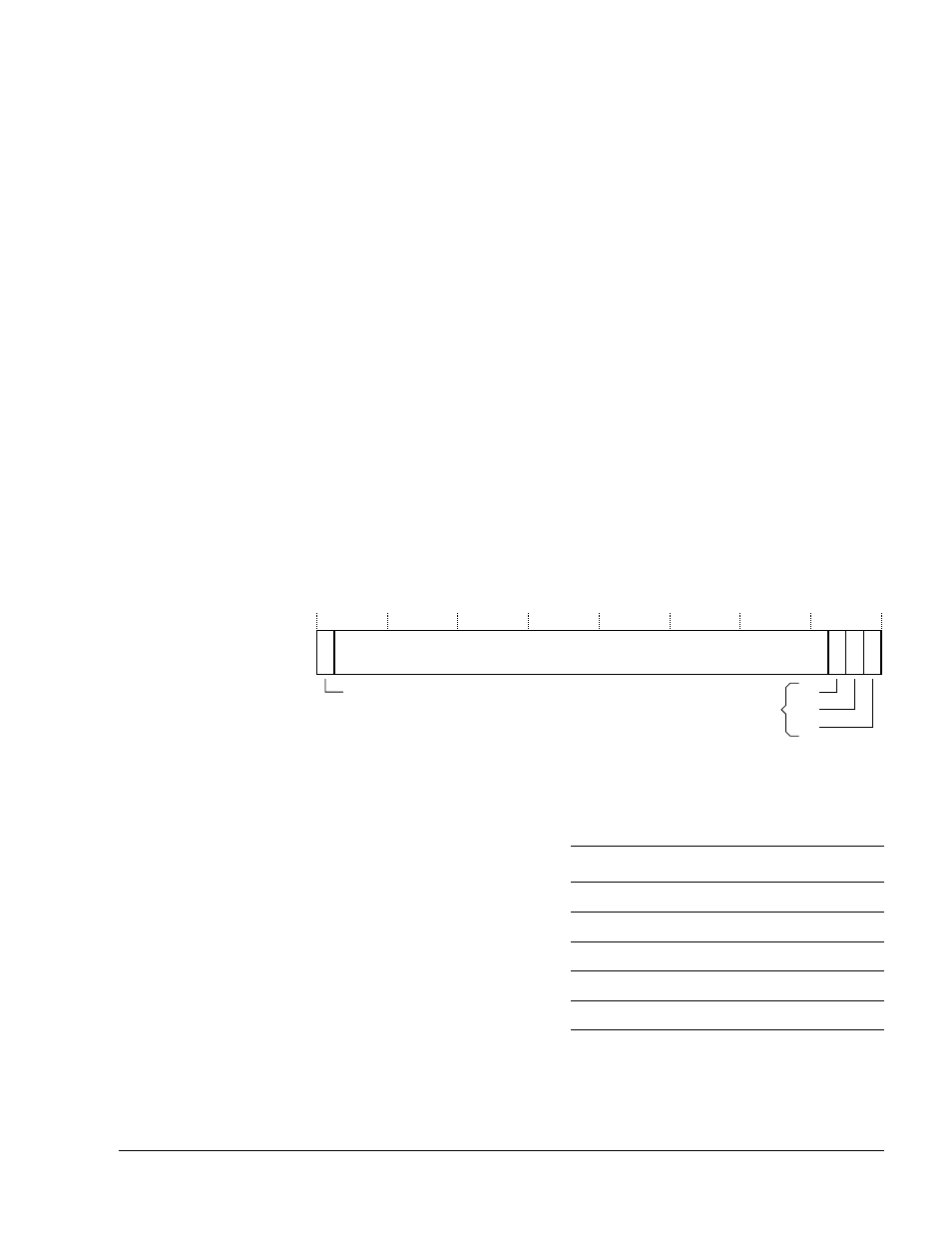

Figure 4-44 shows the bit arrangement for the nVAL IRQ Enable Set Register.

Figure 4-44 nVAL IRQ Enable Set Register format

Table 4-42 shows how the bit values correspond with the nVAL IRQ Enable Set Register.

To access the nVAL IRQ Enable Set Register, read or write CP15 with:

MRC p15, 0,

MCR p15, 0,

C

31

3 2 1 0

Reserved

P2

P1

P0

Performance monitor counter

overflow IRQ request enables

Cycle count overflow IRQ request enable

Table 4-42 nVAL IRQ Enable Set Register bit functions

Bits Field Function

[31]

C

CCNT overflow IRQ request

[30: 3]

Reserved

UNP or SBZP

[2]

P2

PMC2 overflow IRQ request

[1]

P1

PMC1 overflow IRQ request

[0]

P0

PMC0 overflow IRQ request