Table 4-33, Table 4-34, Access data permission bit encoding -52 – ARM Cortex R4F User Manual

Page 136: Figure 4-36, Mpu region access control register format -52

System Control Coprocessor

ARM DDI 0363E

Copyright © 2009 ARM Limited. All rights reserved.

4-52

ID013010

Non-Confidential, Unrestricted Access

The MPU Region Access Control Registers are:

•

read/write registers

•

accessible in Privileged mode only.

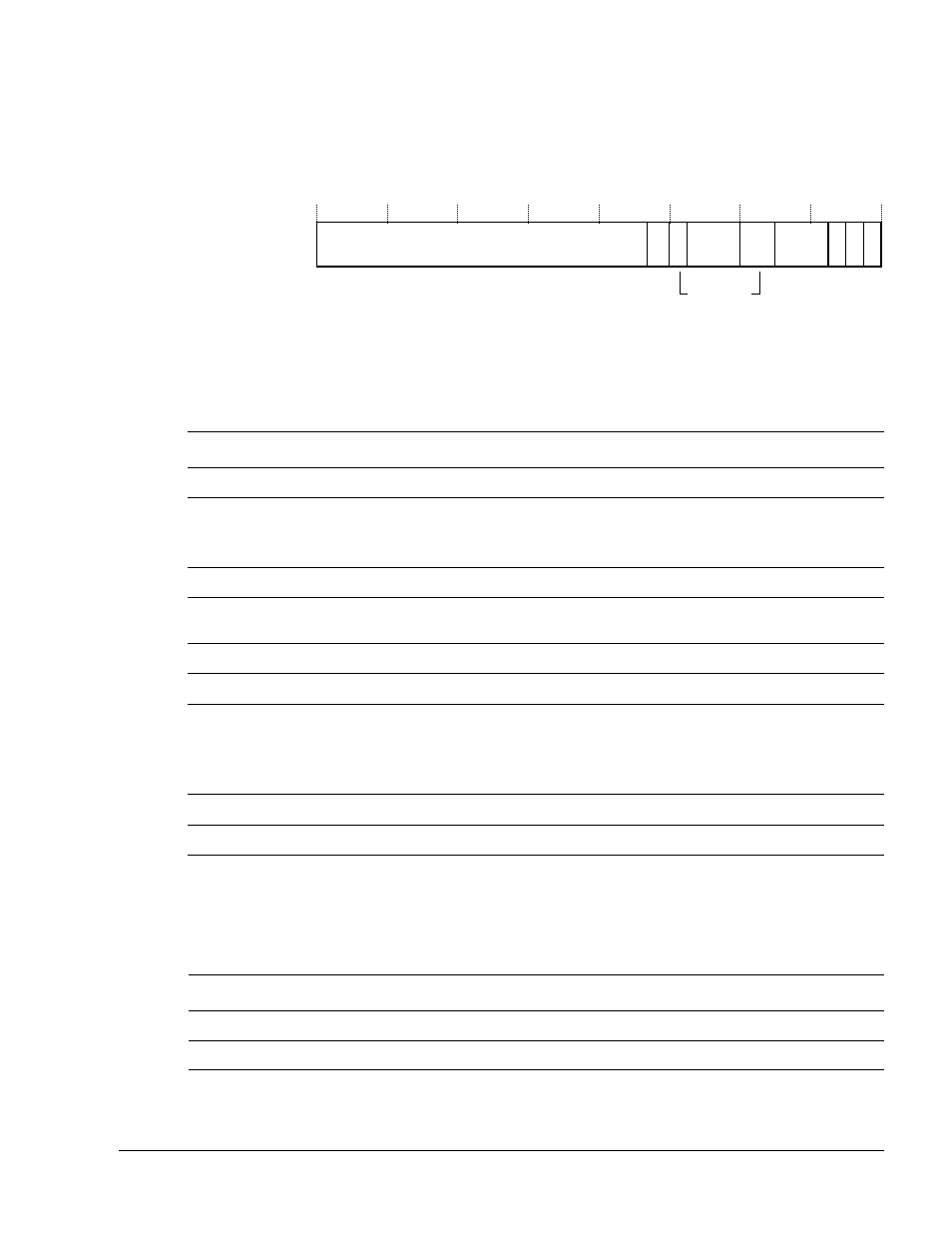

Figure 4-36 shows the arrangement of bits in the register.

Figure 4-36 MPU Region Access Control Register format

Table 4-33 shows how the bit values correspond with the Region Access Control Register

functions.

Table 4-34 shows the AP bit values that determine the permissions for Privileged and User data

access.

Reserved

B

C

31

3

0

TEX

S

1

2

5

6

7

8

11 10

12

XN

AP

Reserved

13

Table 4-33 MPU Region Access Control Register bit functions

Bits

Field

Function

[31:13] Reserved

SBZ.

[12]

XN

Execute never. Determines if a region of memory is executable:

0 = all instruction fetches enabled

1 = no instruction fetches enabled.

[11]

-

Reserved.

[10:8]

AP

Access permission. Defines the data access permissions. For more information on AP bit values

see, Table 4-34.

[7:6]

Reserved

SBZ.

[5:3]

TEX

Type extension. Defines the type extension attribute

a

.

[2]

S

Share. Determines if the memory region is Shared or Non-shared:

0 = Non-shared.

1 = Shared.

This bit only applies to Normal, not Device or Strongly Ordered memory.

[1]

C

C bit

[0]

B

B bit

a. For more information on this region attribute, see Table 7-3 on page 7-9.

Table 4-34 Access data permission bit encoding

AP bit values

Privileged permissions

User permissions

Description

b000

No access

No access

All accesses generate a permission fault

b001

Read/write

No access

Privileged access only

b010

Read/write

Read-only

Writes in User mode generate permission

faults