Test configurations, Design considerations, Austin lynx – GE Industrial Solutions Austin Lynx II SIP User Manual

Page 10: Input filtering, Lineage power 10, Figure 25. output ripple and noise test setup

Data Sheet

October 2, 2009

Austin Lynx

TM

II

SIP Non-isolated Power Modules:

2.4 – 5.5Vdc input; 0.75Vdc to 3.63Vdc Output; 10A output current

LINEAGE

POWER

10

Test Configurations

TO OSCILLOSCOPE

CURRENT PROBE

L

TEST

1μH

B

A

TTE

R

Y

C

S

1000μF

Electrolytic

E.S.R.<0.1

Ω

@ 20°C 100kHz

2x100μF

Tantalum

V

IN

(+)

COM

NOTE: Measure input reflected ripple current with a simulated

source inductance (L

TEST

) of 1μH. Capacitor C

S

offsets

possible battery impedance. Measure current as shown

above.

C

IN

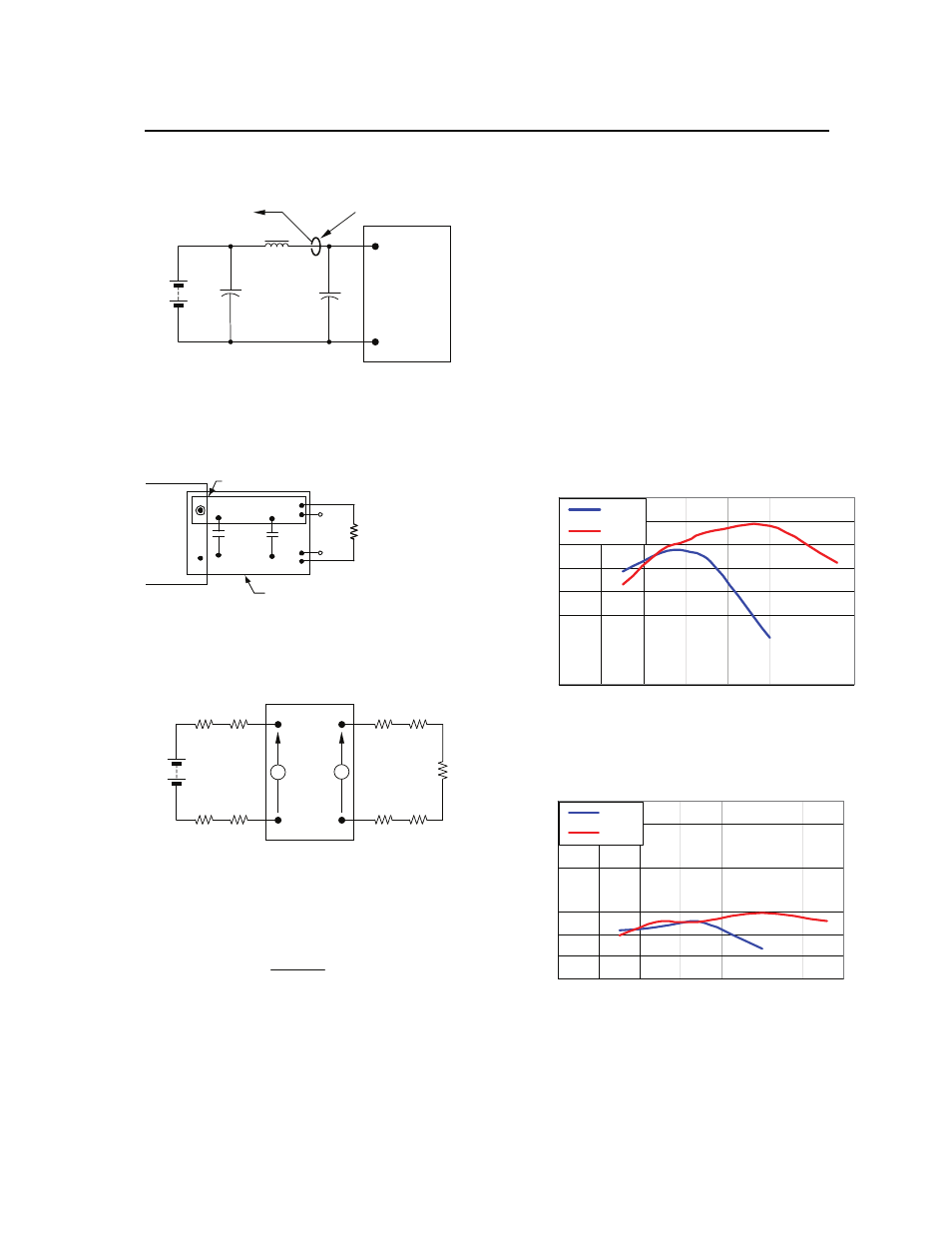

Figure 24. Input Reflected Ripple Current Test

Setup.

NOTE: All voltage measurements to be taken at the module

terminals, as shown above. If sockets are used then

Kelvin connections are required at the module terminals

to avoid measurement errors due to socket contact

resistance.

V

O

(+)

COM

1uF

.

RESISTIVE

LOAD

SCOPE

COPPER STRIP

GROUND PLANE

10uF

Figure 25. Output Ripple and Noise Test Setup.

V

O

COM

V

IN

(+)

COM

R

LOAD

R

contact

R

distribution

R

contact

R

distribution

R

contact

R

contact

R

distribution

R

distribution

V

IN

V

O

NOTE: All voltage measurements to be taken at the module

terminals, as shown above. If sockets are used then

Kelvin connections are required at the module terminals

to avoid measurement errors due to socket contact

resistance.

Figure 26. Output Voltage and Efficiency Test Setup.

η =

V

O

. I

O

V

IN

. I

IN

x

100

%

Efficiency

Design Considerations

Input Filtering

Austin Lynx

TM

II SIP module should be connected to a

low-impedance source. A highly inductive source can

affect the stability of the module. An input capacitance

must be placed directly adjacent to the input pin of the

module, to minimize input ripple voltage and ensure

module stability.

To minimize input voltage ripple, low-ESR polymer and

ceramic capacitors are recommended at the input of the

module. Figure 27 shows input ripple voltage (mVp-p)

for various outputs with 1x150 µF polymer capacitors

(Panasonic p/n: EEFUE0J151R, Sanyo p/n:

6TPE150M) in parallel with 1 x 47 µF ceramic capacitor

(Panasonic p/n: ECJ-5YB0J476M, Taiyo- Yuden p/n:

CEJMK432BJ476MMT) at full load. Figure 28 shows

the input ripple with 3x150 µF polymer capacitors in

parallel with 2 x 47 µF ceramic capacitor at full load.

Input

Ri

ppl

e

Vol

tage (mVp-

p

)

0

10

20

30

40

50

60

70

80

0

0.5

1

1.5

2

2.5

3

3.5

3.3Vin

5Vin

Output

Voltage

(Vdc)

Figure 27. Input ripple voltage for various output

with 1x150 µF polymer and 1x47 µF ceramic

capacitors at the input (full load)

Input

Ri

ppl

e Vol

tage (mVp-

p

)

0

10

2 0

3 0

4 0

50

6 0

70

8 0

0

0 .5

1

1.5

2

2 .5

3

3 .5

3.3Vin

5Vin

Output

Voltage

(Vdc)

Figure 28. Input ripple voltage for various output

with 3x150 µF polymer and 2x47 µF ceramic

capacitors at the input (full load)