Max3107 spi/i, C uart with 128-word fifos and internal oscillator – Rainbow Electronics MAX3107 User Manual

Page 36

36 _____________________________________________________________________________________

MAX3107

SPI/I

2

C UART with 128-Word FIFOs

and Internal Oscillator

Bits 7–4: RxTrig[3:0]

These 4 bits allow definition of the receive FIFO threshold level at which an ISR[3] interrupt is generated. This can be

used to signal that the receive FIFO is nearing overflow or that a predefined number of FIFO locations are available for

being read out in one block.

The actual FIFO trigger level is 8 times RxTrig[7:4], hence, the selectable threshold granularity is eight.

Bits 3–0: TxTrig[3:0]

These 4 bits allow definition of the transmit FIFO threshold level at which the MAX3107 generates an ISR[4] interrupt.

This can be used to manage data flow to the transmit FIFO. For example, if the trigger level is defined near the bottom

of the TxFIFO, the host knows that a predefined number of FIFO locations are available for being written to in one block.

Alternatively, if the trigger level is set near the top of the FIFO, the host is warned when the transmit FIFO is nearing

overflow, if written to on a word-by-word basis.

The actual FIFO trigger level is 8 times TxTrig[3:0], hence, the selectable threshold granularity is eight.

Bits 7–0: TxFL[7:0]

The TxFIFOLvl register represents the current number of words in the transmit FIFO.

Bits 7–0: RxFL[7:0]

The RxFIFOLvl register represents the current number of words in the receive FIFO.

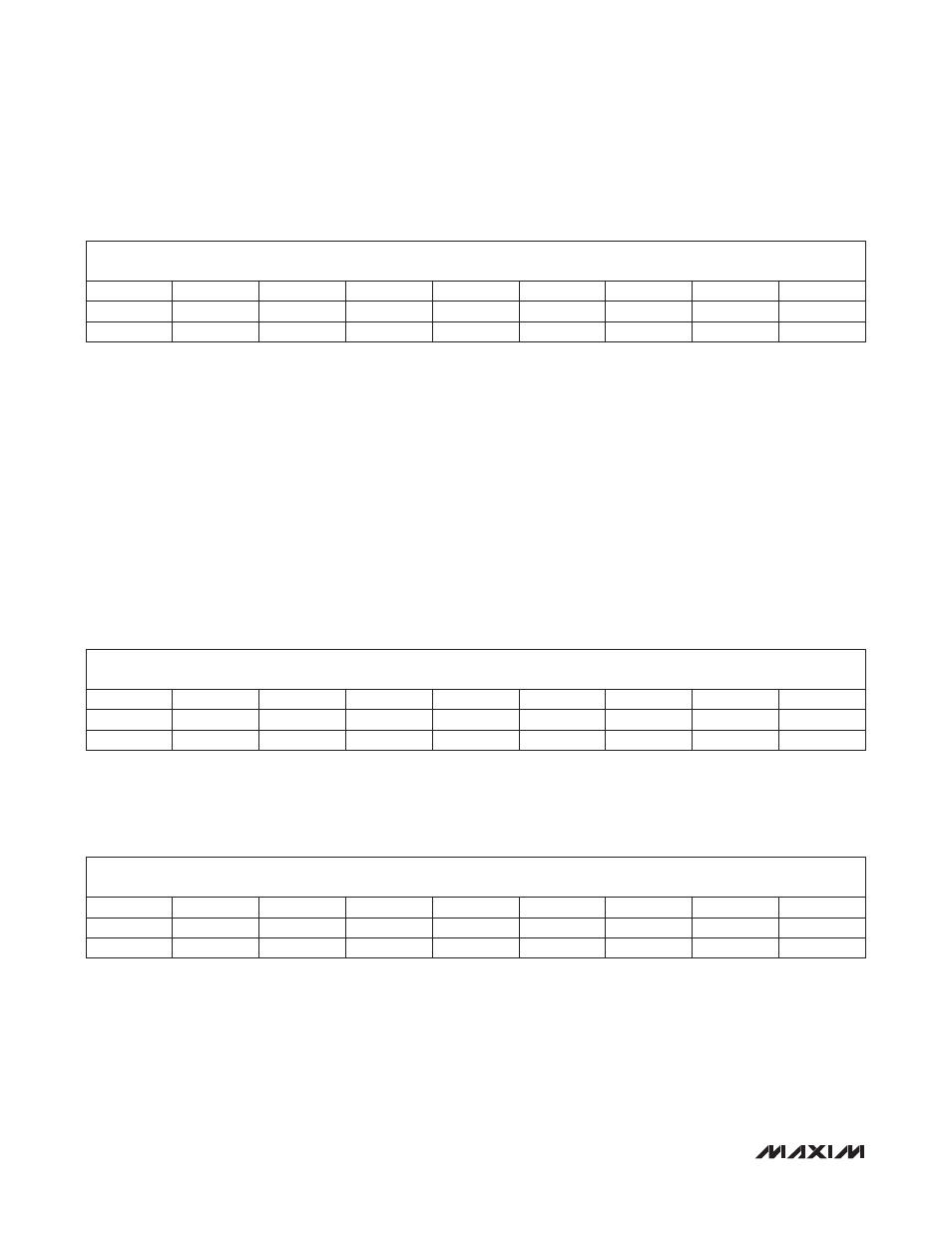

FIFOTrgLvl—FIFO Interrupt Trigger Level Register

TxFIFOLvl—Transmit FIFO Level Register

RxFIFOLvl—Receive FIFO Level Register

ADDRESS:

0x10

MODE:

R/W

BIT

7

6

5

4

3

2

1

0

NAME

RxTrig3

RxTrig2

RxTrig1

RxTrig0

TxTrig3

TxTrig2

TxTrig1

TxTrig0

RESET

1

1

1

1

1

1

1

1

ADDRESS:

0x11

MODE:

R

BIT

7

6

5

4

3

2

1

0

NAME

TxFL7

TxFL6

TxFL5

TxFL4

TxFL3

TxFL2

TxFL1

TxFL0

RESET

0

0

0

0

0

0

0

0

ADDRESS:

0x12

MODE:

R

BIT

7

6

5

4

3

2

1

0

NAME

RxFL7

RxFL6

RxFL5

RxFL4

RxFL3

RxFL2

RxFL1

RxFL0

RESET

0

0

0

0

0

0

0

0