Spclcharint—special character interrupt register, Max3107 spi/i, C uart with 128-word fifos and internal oscillator – Rainbow Electronics MAX3107 User Manual

Page 29

______________________________________________________________________________________ 29

MAX3107

SPI/I

2

C UART with 128-Word FIFOs

and Internal Oscillator

Bits 7 and 6: No Function

Bit 5: MultiDropInt

The MultiDropInt interrupt is set when the MAX3107 receives an address character in 9-bit multidrop mode

(MODE2[6] is 1). This bit is cleared when SpclCharInt is read. The SpclCharInt bit can be routed to ISR[1] by enabling

SpclChrIntEn[5].

Bit 4: BREAKInt

The BreakInt interrupt is set when a line BREAK (RX low for longer than one character length) is detected by the

receiver. This bit is cleared after SpclCharInt is read. The BREAKInt interrupt can be routed to ISR[1] by enabling

SpclChrIntEn[4].

Bit 3: XOFF2Int

The XOFF2Int interrupt bit is set when an XOFF2 special character is received and special character detection is

enabled, through MODE2[4]. This interrupt is cleared upon reading SpclCharInt. The XOFF2Int interrupt can be routed

to the ISR[1] interrupt bit, if enabled through SpclChrIntEn[3].

Bit 2: XOFF1Int

The XOFF1Int interrupt bit is set when an XOFF1 special character is received and special character detection is

enabled, through MODE2[4]. This interrupt is cleared upon reading SpclCharInt. The XOFF1Int interrupt can be routed

to the ISR[1] interrupt bit, if enabled through SpclChrIntEn[2].

Bit 1: XON2Int

The XON2Int interrupt bit is set when an XON2 special character is received and special character detection is

enabled, through MODE2[4]. This interrupt is cleared upon reading SpclCharInt. The XON2Int interrupt can be routed

to the ISR[1] interrupt bit, if enabled through SpclChrIntEn[1].

Bit 0: XON1Int

The XON1Int interrupt bit is set when an XON1 special character is received and special character detection is

enabled, through MODE2[4]. This interrupt is cleared upon reading SpclCharInt. The XON1Int interrupt can be routed

to the ISR[1] interrupt bit, if enabled through SpclChrIntEn[0].

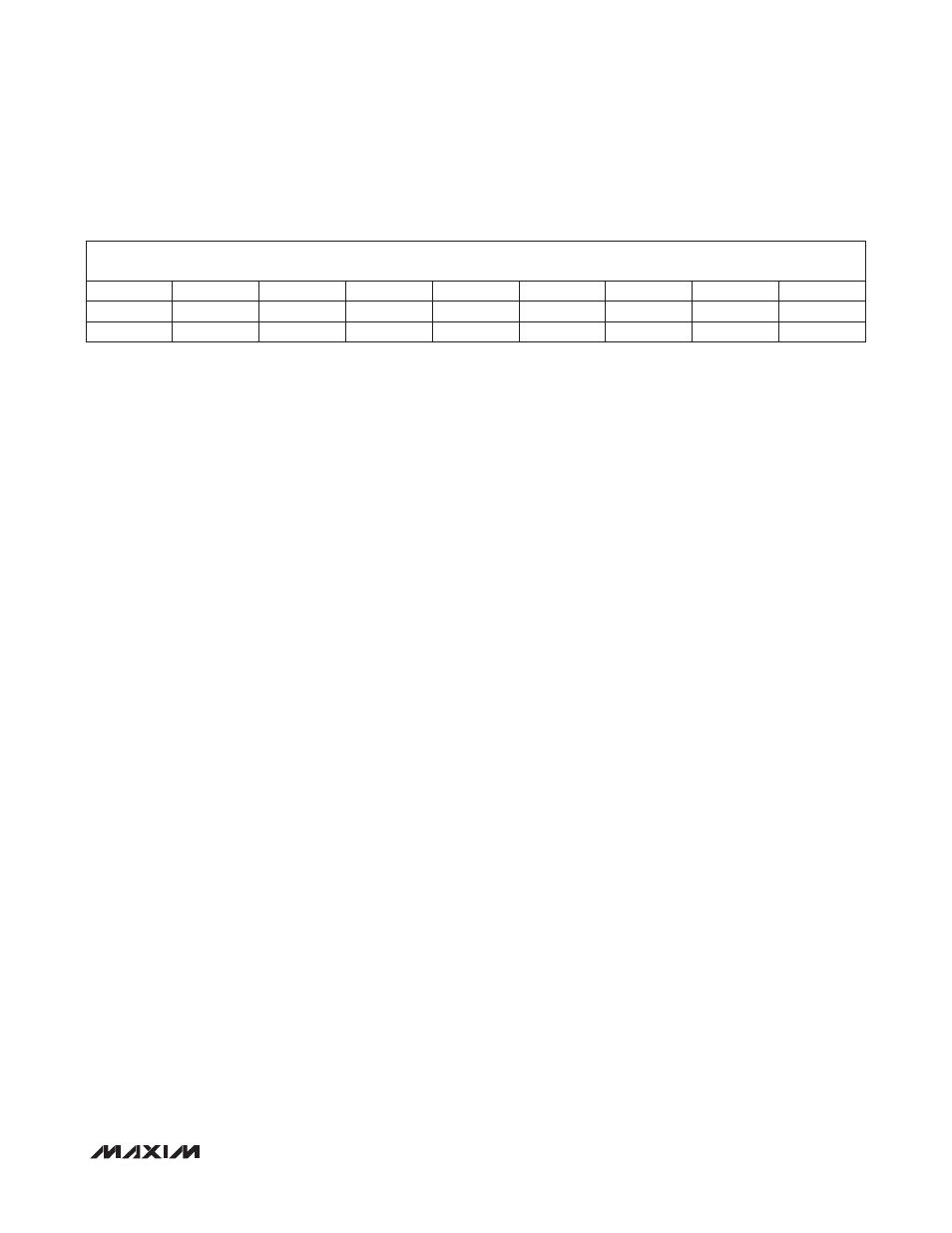

SpclCharInt—Special Character Interrupt Register

ADDRESS:

0x06

MODE:

COR

BIT

7

6

5

4

3

2

1

0

NAME

—

—

MultiDropInt

BREAKInt

XOFF2Int

XOFF1Int

XON2Int

XON1Int

RESET

0

0

0

0

0

0

0

0