Software interrupts, Hardware interrupts, Atar862-4 – Rainbow Electronics ATAR862-4 User Manual

Page 20

20

ATAR862-4

4552B–4BMCU–02/03

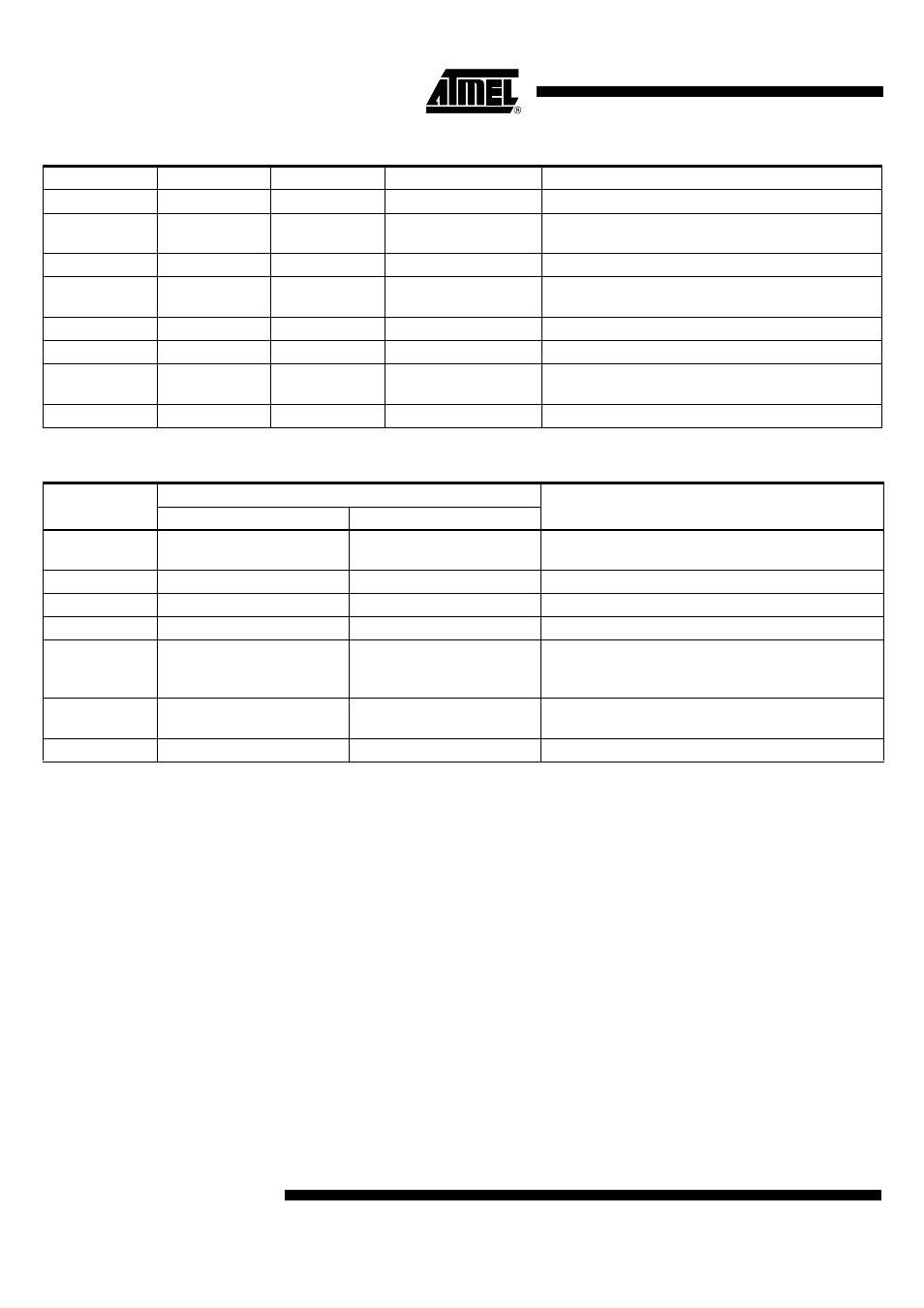

Table 2.

Interrupt Priority Table

Table 3.

Hardware Interrupts

Software Interrupts

The programmer can generate interrupts by using the software interrupt instruction

(SWI), which is supported in qFORTH by predefined macros named SWI0...SWI7. The

software triggered interrupt operates exactly like any hardware triggered interrupt. The

SWI instruction takes the top two elements from the expression stack and writes the cor-

responding bits via the I/O bus to the interrupt pending register. Therefore, by using the

SWI instruction, interrupts can be re-prioritized or lower priority processes scheduled for

later execution.

Hardware Interrupts

In the microcontroller block, there are eleven hardware interrupt sources with seven dif-

ferent levels. Each source can be masked individually by mask bits in the corresponding

control registers. An overview of the possible hardware configurations is shown in

Table 3.

Interrupt

Priority

ROM Address

Interrupt Opcode

Function

INT0

Lowest

040h

C8h (SCALL 040h)

Software interrupt (SWI0)

INT1

|

080h

D0h (SCALL 080h)

External hardware interrupt, any edge at BP52 or

BP53

INT2

|

0C0h

D8h (SCALL 0C0h)

Timer 1 interrupt

INT3

|

100h

E8h (SCALL 100h)

SSI interrupt or external hardware interrupt at BP40

or BP43

INT4

|

140h

E8h (SCALL 140h)

Timer 2 interrupt

INT5

|

180h

F0h (SCALL 180h)

Timer 3 interrupt

INT6

|

1C0h

F8h (SCALL 1C0h)

External hardware interrupt, at any edge at BP50 or

BP51

INT7

Highest

1E0h

FCh (SCALL 1E0h)

Voltage monitor (VM) interrupt

Interrupt

Interrupt Mask

Interrupt Source

Register

Bit

INT1

P5CR

P52M1, P52M2

P53M1, P53M2

Any edge at BP52

any edge at BP53

INT2

T1M

T1IM

Timer 1

INT3

SISC

SIM

SSI buffer full/empty or BP40/BP43 interrupt

INT4

T2CM

T2IM

Timer 2 compare match/overflow

INT5

T3CM1

T3CM2

T3C

T3IM1

T3IM2

T3EIM

Timer 3 compare register 1 match

Timer 3 compare register 2 match

Timer 3 edge event occurs (T3I)

INT6

P5CR

P50M1, P50M2

P51M1, P51M2

Any edge at BP50,

any edge at BP51

INT7

VCM

VIM

External/internal voltage monitoring