Rainbow Electronics DS2432 User Manual

Page 18

PRELIMINARY

DS2432

18 of 30

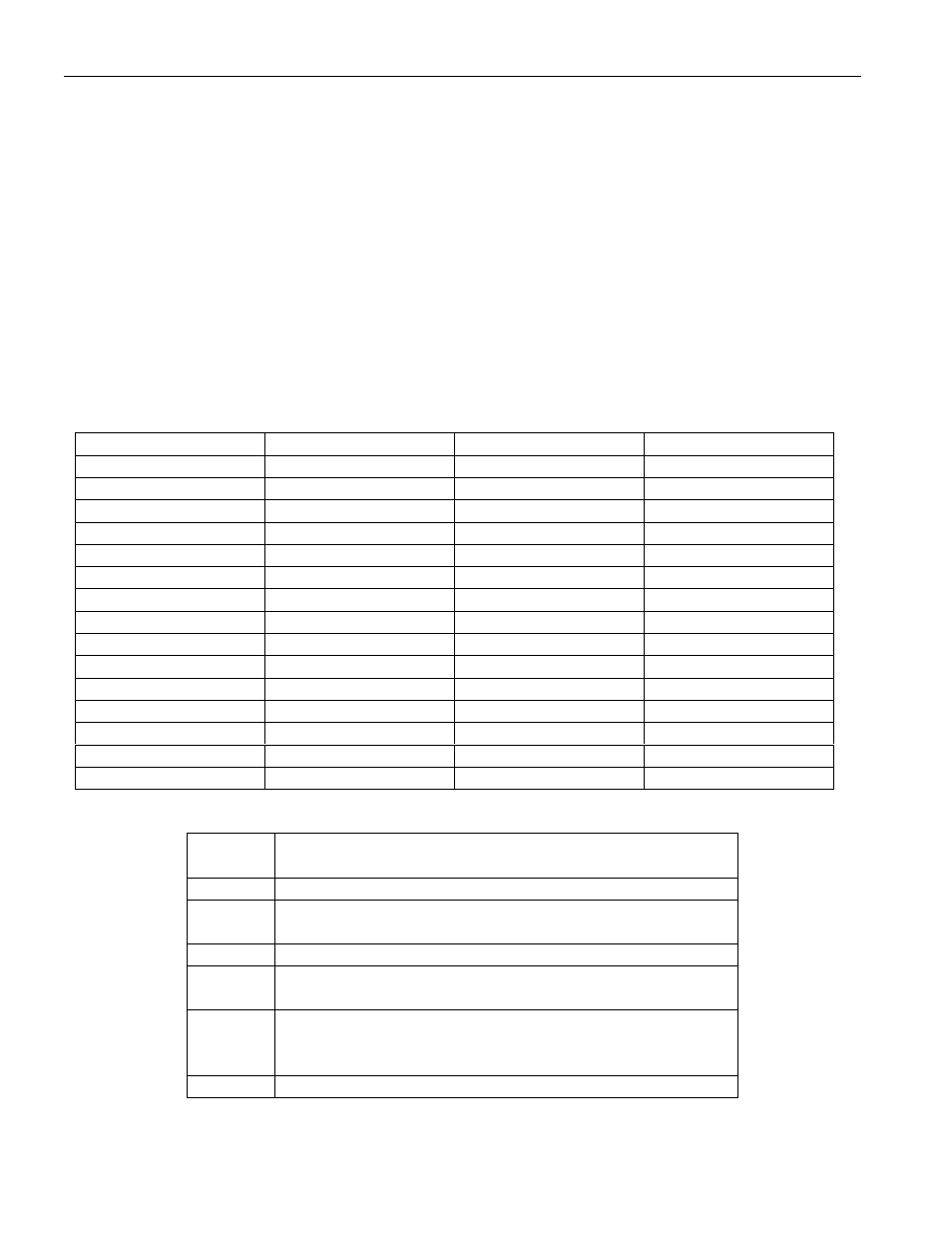

that happens to reside in the scratchpad from a previous command as a challenge. The 160-bit MAC is

transmitted in the same way as with the Copy Scratchpad command, Table 2, but the data flows from the

DS2432 to the master. The data input to the SHA engine as it applies to the Read Authenticated Page

command is shown in Table 4.

After the master has issued the command code and specified a valid target address it will receive the page

data beginning at the target address through the end of the data page, one byte FFh and the inverted CRC

of the command code, target address, transmitted page data and FFh byte. Immediately after the CRC is

received the master waits for 2.0 ms during which the voltage on the 1-Wire bus must not fall below

2.8V. During this time the SHA engine of the DS2432 computes the message authentication code over

the secret, all 32 data bytes of the selected page, the device’s registration number (without the CRC) and

the 3-byte challenge. Now the master reads the 160-bit MAC, which is followed by an inverted CRC as a

means to safeguard the data transfer. If the master continues reading after the CRC it will receive a

pattern of alternating 0’s and 1’s until it issues a Reset Pulse.

SHA-1 Input Data for Read Authenticated Page Command Table 4

M0[31:24] = (SS+0)

M0[23:16] = (SS+1)

M0[15:8] = (SS+2)

M0[7:0] = (SS+3)

M1[31:24] = (PP+0)

M1[23:16] = (PP+1)

M1[15:8] = (PP+2)

M1[7:0] = (PP+3)

M2[31:24] = (PP+4)

M2[23:16] = (PP+5)

M2[15:8] = (PP+6)

M2[7:0] = (PP+7)

M3[31:24] = (PP+8)

M3[23:16] = (PP+9)

M3[15:8] = (PP+10)

M3[7:0] = (PP+11)

M4[31:24] = (PP+12)

M4[23:16] = (PP+13)

M4[15:8] = (PP+14)

M4[7:0] = (PP+15)

M5[31:24] = (PP+16)

M5[23:16] = (PP+17)

M5[15:8] = (PP+18)

M5[7:0] = (PP+19)

M6[31:24] = (PP+20)

M6[23:16] = (PP+21)

M6[15:8] = (PP+22)

M6[7:0] = (PP+23)

M7[31:24] = (PP+24)

M7[23:16] = (PP+25)

M7[15:8] = (PP+26)

M7[7:0] = (PP+27)

M8[31:24] = (PP+28)

M8[23:16] = (PP+29)

M8[15:8] = (PP+30)

M8[7:0] = (PP+31)

M9[31:24] = FFh

M9[23:16] = FFh

M9[15:8] = FFh

M9[7:0] = FFh

M10[31:24] = MP

M10[23:16] = FAMC

M10[15:8] = SN0

M10[7:0] = SN1

M11[31:24] = SN2

M11[23:16] = SN3

M11[15:8] = SN4

M11[7:0] = SN5

M12[31:24] = (SS+4)

M12[23:16] = (SS+5)

M12[15:8] = (SS+6)

M12[7:0] = (SS+7)

M13[31:24] = (SP+4)

M13[23:16] = (SP+5)

M13[15:8] = (SP+6)

M13[7:0] = 80h

M14[31:24] = 00h

M14[23:16] = 00h

M14[15:8] = 00h

M14[7:0] = 00h

M15[31:24] = 00h

M15[23:16] = 00h

M15[15:8] = 01h

M15[7:0] = B8h

Legend

Mt

Input buffer of SHA engine

0

≤

t

≤

15; 32-bit words

SS

Starting address of secret (80h)

PP

Starting address of memory page

See Memory Map, memory pages 0 through 3

FAMC

Family Code = 33h

MP

MP[7:4] = 0100

MP[3:0] = T8:T5 (equivalent to page number in hex)

SNx

ROM Serial number of device

SN0 = least significant byte, SN5 = most significant byte

The CRC is not used

(SP+n)

Byte n of Scratchpad